Une sonde embarquée dans une chaussure pour tricher aux Échecs

Je reprends ici les travaux de Jack Hollingsworth dans son article sur instructables.com : Von Niemann Probe (Licence CC BY-NC-SA)

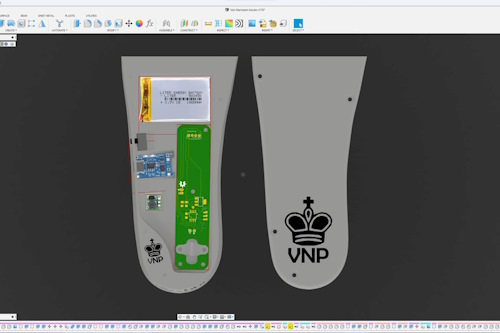

Cette talonnette connectée en Bluetooth peut vibrer discrètement dans la chaussure du joueur d'échecs qui est alors informé en direct et à distance du meilleur coup à jouer.

La talonnette embarque

Ce n'est pas la caractéristique la plus amusante des Arduino Uno R4, mais c'est quand même celle qui risque d'endommager votre carte si vous passez à côté...

Une caractéristique importante est le courant maximum que peut conduire une broche d'entrée-sortie numérique (ou DC current per I/O pin) :

Extraits docs. Arduino Uno R3 et R4

Et le moins qu'on puisse dire, c'est que le seuil de tolérance pour une broche numérique est

En Verilog/SystemVerilog, on peut trouver ce genre de code :

Mais que fait ce code ? Il renvoie Vrai si a est inférieur ou égal à b... Non, ce n'est pas ça. Le signe <= est surement un opérateur d'affectation : je mets b dans a... puis a dans b ? C'est pour échanger les valeurs de a et b (swap)

Code SystemVerilog : Sélectionner tout - Visualiser dans une fenêtre à part

2? Mais ça ne peut pas fonctionner, car « normalement » pour faire l'échange, il faut passer par une variable temporaire :

Code C : Sélectionner tout - Visualiser dans une fenêtre à part temp = a; a = b; b = temp;

En logique combinatoire, les sorties d'un système numérique ne dépendent que des états logiques présents aux entrées. Le système n'a donc pas de mémoire, et un système sans mémoire est forcément très limité.

Prenez l'exemple d'un système d'ouverture à code qui donne trois tentatives à l'utilisateur pour saisir le bon code. Dans un système à logique purement combinatoire, chaque saisie de code infructueuse ne peut produire qu'un seul résultat, car sans mémorisation, il ne peut pas tenir compte

Lors du billet précédent, nous avions vu comment établir la description d'un composant simple appelé multiplexeur :

Si sel=0, a est dirigé vers s, et si sel=1, c'est b qui est dirigé vers s

Au niveau d'abstraction le plus bas, le niveau structurel, ce composant est décrit par le câblage de portes logiques élémentaires (portes AND, OR et NOT dans ce cas précis). Voyons comment pourrait-on établir une description de ce composant à

Vous avez un bloqueur de publicités installé.

Le Club Developpez.com n'affiche que des publicités IT, discrètes et non intrusives.

Afin que nous puissions continuer à vous fournir gratuitement du contenu de qualité, merci de nous soutenir en désactivant votre bloqueur de publicités sur Developpez.com.