Les processeurs Intel x86 souffriraient d'un défaut

Qui exposerait la mémoire noyau et impacterait surtout le marché serveur

Des rapports circulant depuis quelques jours sur la toile font état dune vulnérabilité qui affecterait de manière spécifique (cest encore spéculatif) les processeurs modernes de lentreprise américaine Intel (génération ≥ Pentium Pro). Cette vulnérabilité pourrait être considérée comme majeure parce quelle mettrait en exergue un éventuel problème de sécurité sur les processeurs Intel suffisamment grave pour obliger Microsoft et Linus Torvalds à produire à la hâte des patchs spécifiques pour leurs OS respectifs.

Si au départ la vulnérabilité, telle quelle avait été rapportée, avait pu faire croire que lensemble des processeurs exploitant larchitecture x86 64-bits étaient concernés, une déclaration récente dAMD a permis de voir un peu plus clair dans cette affaire.

« Les processeurs AMD ne sont pas concernés par les attaques contre lesquelles les techniques disolation de la table du noyau protègent. La microarchitecture AMD nautorise pas les références mémoire, y compris les exécutions spéculatives, qui tentent daccéder à des données à privilèges plus élevés alors quelles sexécutent dans un mode privilégié inférieur quand cet accès est susceptible dentraîner une erreur », pouvait-on lire dans le communiqué de la firme de Sunnyvale.

On pourrait donc supposer que la firme de Sunnyvale dispose dinformations encore sous embargo pour clamer ne pas être concernée même sil faut éviter de tirer des conclusions hâtives tant que toute la lumière naura pas été faite sur cette affaire et les détails rendus publics. Au passage, il faut signaler que les processeurs basés sur les architectures ARM/RISC ne semblent pas être affectés.

Lexécution spéculative est essentiellement une forme de préemption qui tente de prédire quel code va être exécuté après un branchement, puis de lextraire et de lexécuter avant que lordre réel narrive. Les processeurs modernes ont une architecture en pipeline : ils traitent un grand nombre d'instructions simultanément, en avançant un petit peu dans chacune à chaque cycle. Si un branchement est mal prédit, tout le pipeline doit être vidé : la perte en performance est loin d'être négligeable. Cette technique a ses avantages, mais elle présente également un risque non négligeable pour la sécurité, car aucune vérification de privilège nest présente au niveau du noyau du système d'exploitation.

Le problème réside dans le fait que vous pouvez exploiter cette fonctionnalité pour exécuter de manière spéculative un code qui devrait être normalement bloqué en stoppant lexécution du code avant quune vérification puisse être effectuée. Cela signifie en gros quune application de niveau 3 (droits normaux) peut lire les données du noyau de niveau 0 (réservé à l'exécution du noyau) en utilisant une exécution spéculative, car la vérification de privilège ne sera pas effectuée avant que le code ne soit exécuté.

Tout serait parti dun article de blog paru en juillet 2017. Son auteur y décrivait une expérience dans laquelle il tente daccéder à la mémoire protégée utilisée par le noyau à partir de lespace utilisateur, lespace mémoire utilisé par les programmes classiques, en exploitant les mécanismes dexécution spéculative intégrés dans les CPU x86 64-bits modernes.

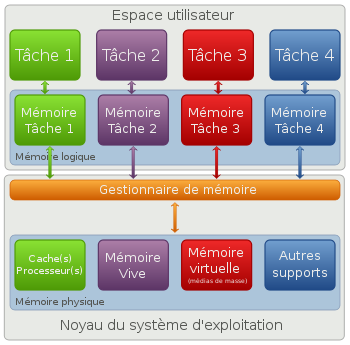

Ces processeurs disposent dunités spécialisées dans la gestion de la mémoire (MMU) qui permettent de contrôler les accès quun CPU fait à la mémoire de lordinateur. Ils peuvent fonctionner suivant au moins deux modes de fonctionnement, dont un mode noyau qui nimpose pas de restrictions sur les instructions exécutées, et un mode utilisateur qui limite ce que peuvent faire les instructions.

Habituellement, le système dexploitation met en uvre cette distinction en faisant fonctionner les autres programmes en mode utilisateur et en se réservant le mode noyau. Cette distinction entre espace utilisateur et espace noyau est à la base du contrôle daccès qui empêche les instructions des applications de lespace utilisateur daccéder à une zone mémoire ne leur appartenant pas. On parle aussi de lecture dune adresse mémoire non autorisée lorsque ce dysfonctionnement survient. Cette situation débouche rapidement sur une trappe du noyau et, en général, la fermeture du programme incriminé. Il faut noter que la trappe est déclenchée par une interruption matérielle et le mécanisme de protection mémoire ne peut être implémenté efficacement de façon logicielle.

Lauteur du blog a essayé de sattaquer à ce mécanisme en tentant dexploiter lintervalle de temps pendant lequel une instruction non autorisée est exécutée et génère une interruption. Même sil a précisé ne pas avoir réussi à lire la mémoire protégée grâce à sa méthode, il sest rendu compte que le chargement mémoire interdit est bel et bien effectué par le CPU même si le processeur ne copie jamais linformation dans le registre. Il a remarqué que lexécution spéculative se poursuivait dans les unités dexécutions internes du CPU jusquà ce que linterruption soit effective et que cette situation pouvait favoriser la survenue dattaques potentielles basées, par exemple, sur les temps dexécution des instructions pour déterminer les adresses mémoires utilisées par le noyau.

Quil soit possible, à partir dun programme utilisateur, de déterminer les adresses mémoire utilisées par le noyau est une situation qui ne devrait pas se produire. Différentes techniques ont dailleurs été mises au point depuis des années pour respecter ce principe, lune des méthodes les plus efficaces à lheure actuelle étant lASLR (Address Space Layout Randomization). Cette dernière attribue un caractère aléatoire aux adresses mémoires utilisées par les applications et le noyau.

Cette « vulnérabilité matérielle » (parce que liée au fonctionnement spécifique des CPU modernes dIntel comme semble le confirmer le mémo dAMD) permettrait dexploiter des processus en espace utilisateur en contournant la MMU et daccéder à la mémoire noyau. Le problème étant matériel, dans la partie non reconfigurable du processeur, il ne serait apparemment pas envisageable de recourir à un patch via microcode pour corriger cette faille de sécurité.

La seule façon de contourner cette fonctionnalité au niveau logiciel serait dutiliser une technique disolation de la table de correspondance (entre les adresses en mémoire virtuelle et en mémoire physique) du noyau (en anglais, KPTI) : cela rendrait le noyau complètement aveugle et le retirerait de lespace mémoire virtuel jusquà ce quun appel système survienne. Il faudrait donc laisser aux éditeurs dOS le soin de concevoir ces patchs via le système dexploitation pour leurs produits respectifs.

À ce propos, il faut signaler que, durant ces derniers mois, KAISER, une nouvelle solution de sécurité proactive dédiée au noyau Linux, a vu le jour. Cette solution, qui a été renommée par la suite KPTI (Kernel Page Table Isolation), est censée limiter de manière significative limpact déventuelles failles présentes ou à venir et mieux protéger les espaces mémoire du noyau. Il permettrait notamment de séparer les tables qui pointent vers les pages mémoires utilisées par le noyau de toutes les autres. Le 30 décembre dernier, Linus Torvalds a intégré KPTI directement dans la version 4.15-rc6 du noyau Linux et recommandé lintégration de ce patch dans tous les noyaux encore maintenus, ce qui pourrait laisser penser que le problème devait être suffisamment grave pour que de telles mesures soient adoptées. Microsoft aurait également préparé des correctifs similaires à KPTI pour le noyau de Windows depuis novembre dernier.

Le problème avec ces patchs, cest quils introduisent une pénalité de temps pour le système et quils ont un impact non négligeable sur les performances de certains types dapplications. Celles qui effectuent beaucoup dappels aux instructions système devraient être les plus affectées. Pour une utilisation non serveur, tout semble pointer vers un impact nul ou infinitésimal. Côté serveur limpact serait plus large et pourrait affecter massivement les infrastructures cloud où la virtualisation, très gourmande en appels système, est largement utilisée.

Source : Cyber WTF, AMD, Twitter info patch Windows, WccfTech

Et vous ?

Quen pensez-vous ?

Voir aussi

Les processeurs Intel x86 souffrent d'un défaut qui permet d'installer des logiciels malveillants dans l'espace protégé des puces

Répondre avec citation

Répondre avec citation

Partager