1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

|

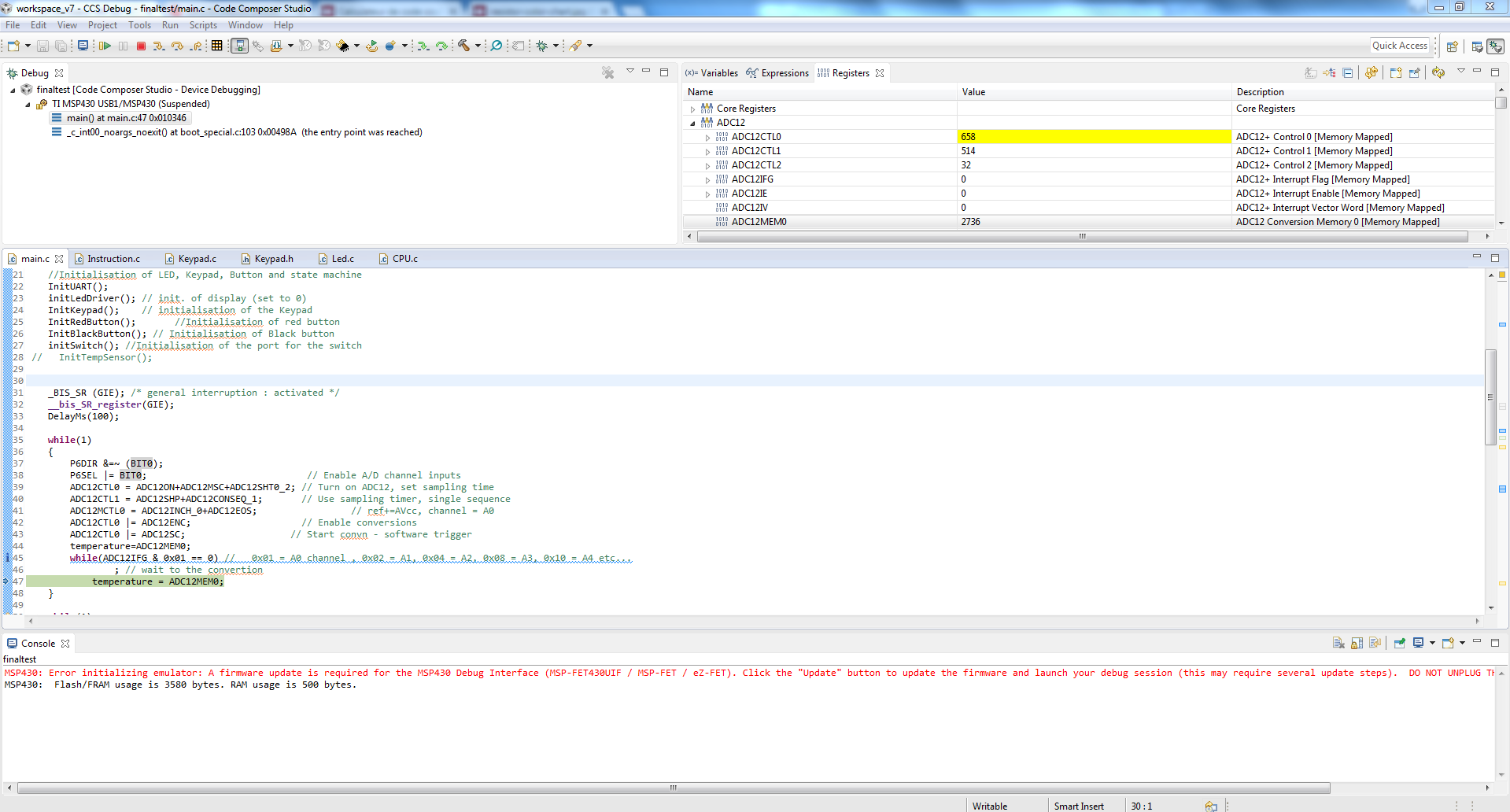

#include <msp430.h>

volatile unsigned int results[4]; // Needs to be global in this example

// Otherwise, the compiler removes it

// because it is not used for anything.

int main(void)

{

WDTCTL = WDTPW+WDTHOLD; // Stop watchdog timer

P6SEL = 0x0F; // Enable A/D channel inputs

ADC12CTL0 = ADC12ON+ADC12MSC+ADC12SHT0_2; // Turn on ADC12, set sampling time

ADC12CTL1 = ADC12SHP+ADC12CONSEQ_1; // Use sampling timer, single sequence

ADC12MCTL0 = ADC12INCH_0; // ref+=AVcc, channel = A0

ADC12MCTL1 = ADC12INCH_1; // ref+=AVcc, channel = A1

ADC12MCTL2 = ADC12INCH_2; // ref+=AVcc, channel = A2

ADC12MCTL3 = ADC12INCH_3+ADC12EOS; // ref+=AVcc, channel = A3, end seq.

ADC12IE = 0x08; // Enable ADC12IFG.3

ADC12CTL0 |= ADC12ENC; // Enable conversions

while(1)

{

ADC12CTL0 |= ADC12SC; // Start convn - software trigger

__bis_SR_register(LPM4_bits + GIE); // Enter LPM4, Enable interrupts

__no_operation(); // For debugger

}

}

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=ADC12_VECTOR

__interrupt void ADC12ISR (void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(ADC12_VECTOR))) ADC12ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(ADC12IV,34))

{

case 0: break; // Vector 0: No interrupt

case 2: break; // Vector 2: ADC overflow

case 4: break; // Vector 4: ADC timing overflow

case 6: break; // Vector 6: ADC12IFG0

case 8: break; // Vector 8: ADC12IFG1

case 10: break; // Vector 10: ADC12IFG2

case 12: // Vector 12: ADC12IFG3

results[0] = ADC12MEM0; // Move results, IFG is cleared

results[1] = ADC12MEM1; // Move results, IFG is cleared

results[2] = ADC12MEM2; // Move results, IFG is cleared

results[3] = ADC12MEM3; // Move results, IFG is cleared

__bic_SR_register_on_exit(LPM4_bits); // Exit active CPU, SET BREAKPOINT HERE

case 14: break; // Vector 14: ADC12IFG4

case 16: break; // Vector 16: ADC12IFG5

case 18: break; // Vector 18: ADC12IFG6

case 20: break; // Vector 20: ADC12IFG7

case 22: break; // Vector 22: ADC12IFG8

case 24: break; // Vector 24: ADC12IFG9

case 26: break; // Vector 26: ADC12IFG10

case 28: break; // Vector 28: ADC12IFG11

case 30: break; // Vector 30: ADC12IFG12

case 32: break; // Vector 32: ADC12IFG13

case 34: break; // Vector 34: ADC12IFG14

default: break;

}

} |

Répondre avec citation

Répondre avec citation

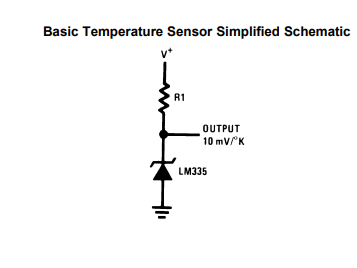

le LM335.

le LM335.

Partager