1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

|

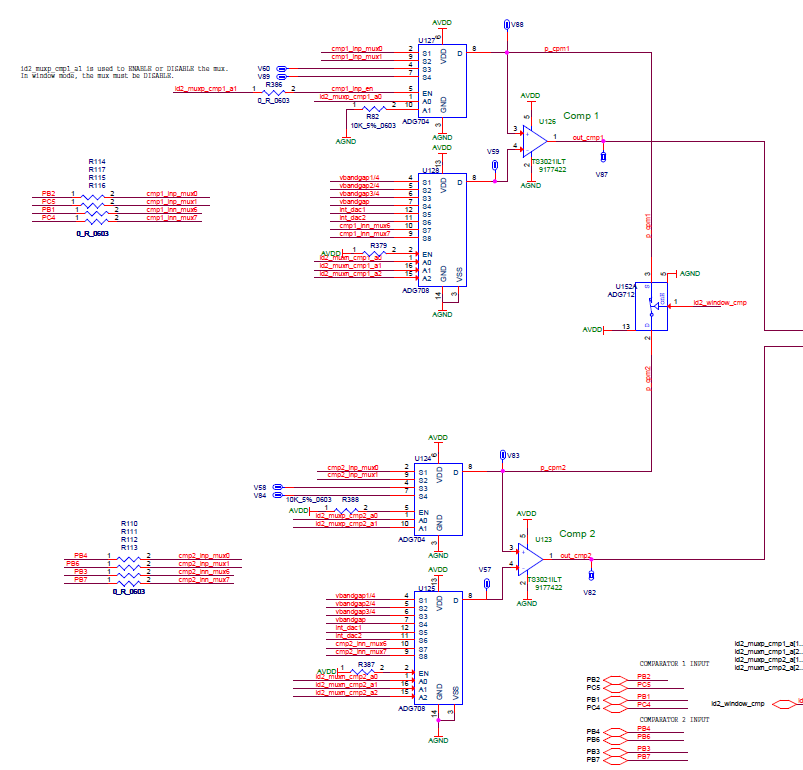

library ieee;

use ieee.std_logic_1164.all;

library analogdevice_lib;

use analogdevice_lib.all;

library st_lib;

use st_lib.all;

entity systeme_comparateur is

port(enable_mux4_comp1,

enable_mux8_comp1,

enable_mux4_comp2,

enable_mux8_comp2 : in std_logic;

A_mux4_comp1,

A_mux4_comp2 : in std_logic_vector (1 downto 0);

A_mux8_comp1,

A_mux8_comp2 : in std_logic_vector (2 downto 0);

S_mux4_comp1,

S_mux4_comp2 : in real_vector (3 downto 0);

S_mux8_comp1,

S_mux8_comp2 : in real_vector (7 downto 0);

In_switch : in std_logic;

Sortie_comp1,

Sortie_comp2 : out real);

end systeme_comparateur;

architecture archi of systeme_comparateur is

component analog_ADG704

generic (INPUTS_SEL: integer);

port(EN : in std_logic;

A : in std_logic_vector (INPUTS_SEL-1 downto 0);

S : in real_vector (2**INPUTS_SEL-1 downto 0);

D : out real);

end component;

component analog_ADG708

generic (INPUTS_SEL: integer);

port(EN : in std_logic;

A : in std_logic_vector (INPUTS_SEL-1 downto 0);

S : in real_vector (2**INPUTS_SEL-1 downto 0);

D : out real);

end component;

component analog_comparateur

generic (vcc : real;

gnd : real);

port(in_pos : in real;

in_neg : in real;

s_comp : out real);

end component;

component analog_ADG712_1

port(In_ADG_1: in std_logic;

D_ADG_1: in real;

S_ADG_1: out real);

end component;

signal int1, int2, int3, int4 : real;

begin

mux4_comp1: analog_ADG704

generic map (INPUTS_SEL => 2)

port map (enable_mux4_comp1,

A_mux4_comp1,

S_mux4_comp1,

int1);

mux8_comp1: analog_ADG708

generic map (INPUTS_SEL => 3)

port map (enable_mux8_comp1,

A_mux8_comp1,

S_mux8_comp1,

int2);

comp1: analog_comparateur

generic map (vcc => 5.0, gnd => 0.0)

port map (int1, int2, Sortie_comp1);

mux4_comp2: analog_ADG704

generic map (INPUTS_SEL => 2)

port map (enable_mux4_comp2,

A_mux4_comp2,

S_mux4_comp2,

int3);

mux8_comp2: analog_ADG708

generic map (INPUTS_SEL => 3)

port map (enable_mux8_comp2,

A_mux8_comp2,

S_mux8_comp2,

int4);

comp2: analog_comparateur

generic map (vcc => 5.0, gnd => 0.0)

port map (int3, int4, Sortie_comp2);

switch: analog_ADG712_1

port map (In_switch, int3, int1);

end archi; |

Répondre avec citation

Répondre avec citation

Partager