3 nm, 5 nm et 7 nm : tour dhorizon des différents procédés de gravure

En cours dexploitation ou en devenir dans lindustrie des semi-conducteurs

Les progrès observés dans lindustrie des semi-conducteurs sont à la base de la conception de puces toujours plus petites et performantes. Les avancées intéressant notamment le procédé de gravure exploité pour la fabrication de ces puces (quil sagisse de microprocesseurs, de mémoires, de circuits logiques programmables, de SoC ou autres) peuvent être considérées comme un facteur clé de cette évolution.

Les entreprises technologiques Samsung Electronics, TSMC, Intel et GlobalFoundries sont des acteurs incontournables de cette industrie puisquils sont impliqués dans le développement des technologies permettant la fabrication des puces et notamment lamélioration de leur finesse de gravure.

Lannée dernière Samsung, GlobalFoundries et IBM ont présenté la première puce gravée en 5 nm et formée de transistors GAAFET, des transistors à nanosheet empilés de type GAA (Gate-All-Around). À peu près pendant la même période, Samsung et TSMC ont communiqué sur leurs futurs processus de fabrication de semi-conducteurs avec des projections sétalant jusquen 2020-2022.

Actuellement, les procédés de gravure les plus utilisés sont le 14 nm (chez Intel notamment), le 12 nm (chez AMD notamment) et le 10 nm (largement répandu dans le marché des puces pour mobiles). On sait également quIntel a du mal à finaliser son procédé de gravure en 10 nm, une technologie qui serait équivalente (du point de vue de la densité) au procédé de gravure en 7 nm de la concurrence, et qu'AMD prévoit de proposer, dès 2019, de nouvelles puces exploitant la technologie de gravure en 7 nm LP développée par Globalfoundries. Lentreprise TSMC, de son côté, a déjà confirmé quelle serait en mesure de proposer sa technologie de gravure en 7 nm (7 FF ou CLN7FF) pour la production de masse dès le deuxième trimestre 2018.

Le site Web semiwiki a comparé les différents procédés de gravure proposés par les fondeurs les plus importants de lindustrie des semi-conducteurs (Samsung, TSMC, Intel et GlobalFoundries) en incluant leurs technologies de gravure respectives en cours de développement.

Avant dexposer les résultats du site, rappelons que le procédé de base permettant de concevoir des circuits intégrés consiste à transposer les fonctions logiques de ce circuit en un ensemble de transistors interconnectés à partir du circuit logique désiré. Cette technique permet dobtenir des cellules élémentaires qui seront par la suite interconnectées pour réaliser la fonction logique proprement dite du circuit désiré. Malheureusement, ce procédé sest révélé inexploitable à partir dun certain degré de complexité de la fonction logique à intégrer.

Lindustrie des semi-conducteurs sest alors tournée vers des systèmes de conception assistée par ordinateur, dans lesquels on utilise des cellules standardisées archivées dans une bibliothèque. Linterconnexion entre ces cellules peut elle-même être réalisée à laide dalgorithmes de câblage exploités par un ordinateur. Il existe à lheure actuelle deux techniques ou systèmes de conception fondés sur ce principe :

- la technique des cellules standard qui consiste à utiliser une bibliothèque de fonctions logiques relativement complexes qui sera par la suite disposée sur la surface disponible dun substrat en tenant compte des interconnexions nécessaires entre elles ;

- la technique dite des réseaux prédiffusés qui consiste à réaliser des ensembles de cellules très simples, identiques entre elles et alignées selon une série de rangées séparées par des espaces libres dune largeur déterminée.

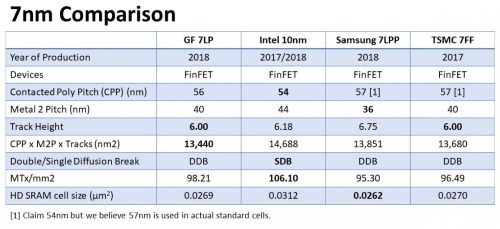

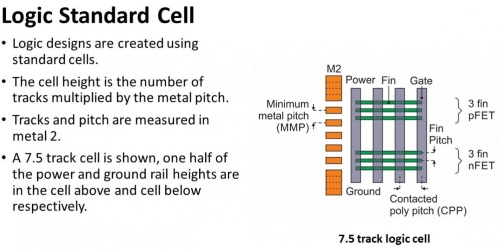

Comme le montre la figure suivante, la taille de chaque cellule standard est déterminée par le Contacted Poly Pitch (CPP), le Metal 2 Pitch (M2P) et le Tracks (le nombre de M2P dans la hauteur dune cellule).

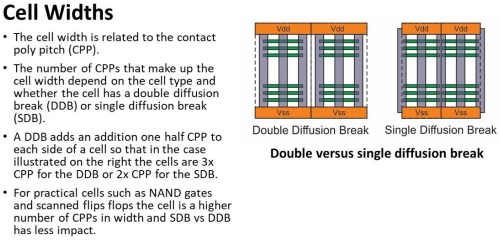

Comme illustré sur la figure ci-dessous, la single diffusion break (SDB), la double diffusion break (DDB) et le CPP détermine, pour leurs parts, la largeur réelle des cellules.

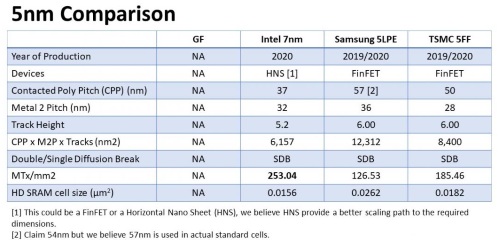

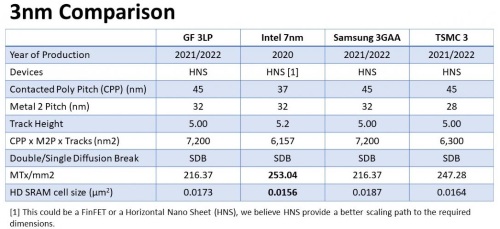

Les tableaux suivants comparent successivement les technologies de gravure en 7, 5 puis 3 nm des fondeurs Samsung Electronics, TSMC, Intel et GlobalFoundries (GF). Ils ne permettent cependant en aucun cas de comparer les performances relatives des puces pouvant exploiter l'un ou l'autre de ces designs. Précisons en outre que l'indice « CPPxM2PxTracks » permet d'apprécier la taille relative de chaque cellule en nm2, alors que l'indice MTx/mm2 se rapporte au nombre de transistors (en millions) par millimètre carré. Ces deux indices donnent un aperçu de la densité réelle pour chacune des technologies de gravure présentées avec, selon SemiWiki, un avantage pour le second indice de mesure.

En se focalisant sur la technologie de gravure en 7 nm des différents fondeurs (incluant le 10 nm dIntel), on peut remarquer que les quatre entreprises technologiques (Samsung, TSMC, Intel et GF) proposent une densité similaire. D'un autre côté, le processus de gravure en 7 nm quIntel envisage de mettre au point semble plus dense et offrirait plus de transistors par mm2 que ceux en 5 nm et 3 nm de ses concurrents.

Cependant, entre projection et réalité un fossé existe bel et bien. Seul lavenir nous dira si Intel sera capable de tenir ses promesses en fournissant ce qui s'apparente au meilleur procédé de gravure du marché, dautant plus que TSMC et Samsung, les fondeurs les plus en vue du moment, semblent être les seuls en mesure de respecter leurs engagements.

Source : SemiWiki, Google

Et vous ?

Quen pensez-vous ?

Voir aussi

Samsung a détrôné Intel sur un marché de semi-conducteurs en hausse de 22,2 %, après un règne qui aura duré 26 ans d'affilée

La prochaine génération de transistors 3D pourrait remettre la loi de Moore au goût du jour, d'après un consortium de l'industrie des semi-conducteurs

Les futurs CPU Xeon Ice Lake d'Intel se dévoilent : 10 nm, nouveau socket LGA4189, plus de curs, TDP en hausse et support de huit canaux mémoires

Intel ne pourra produire des CPU gravés en 10 nm en masse qu'en 2019 et annonce des résultats financiers record au premier trimestre 2018

Répondre avec citation

Répondre avec citation

Partager