Hello

Je vous propose un tutoriel pour apprendre à programmer une carte FPGA dans l'environnement Quartus Prime d'Intel.

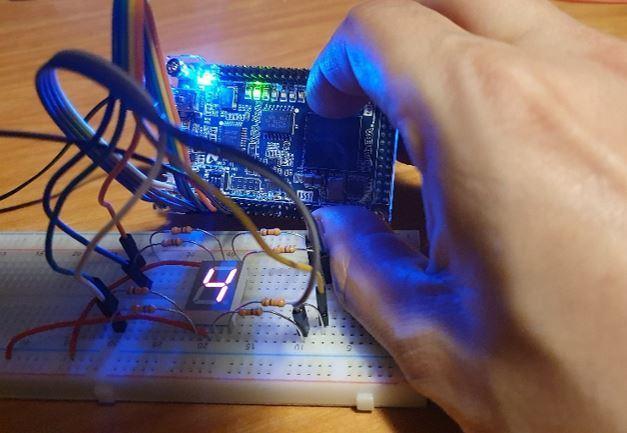

Dans ce tutoriel, on vous propose une petite séance de travaux pratiques avec la suite Quartus Prime dIntel pour programmer une puce FPGA. Lexercice consiste à faire la description dun afficheur 7-segments où sinscrit la valeur dun compteur qui sincrémente à chaque appui sur un bouton-poussoir. La description par schéma-blocs, mais aussi en langage Verilog est présentée. La cible est la carte du kit Terasic DE0-Nano, mais lactivité peut très bien être adaptée à dautres cartes de développement FPGA compatibles avec la suite dIntel.

La cible FPGA est une carte Terasic DE0-Nano (Soc FPGA Intel Cyclone IV)

Bonne lecture, et n'hésitez pas à poster vos commentaires dans ce fil de discussion

Répondre avec citation

Répondre avec citation

Partager