à tous,

Pour cette rentrée, je vous propose ce tutoriel pour apprendre à configurer un contrôleur décran VGA sur une carte de développement FPGA :

Programmer un contrôleur pour écran VGA avec une carte de développement FPGA

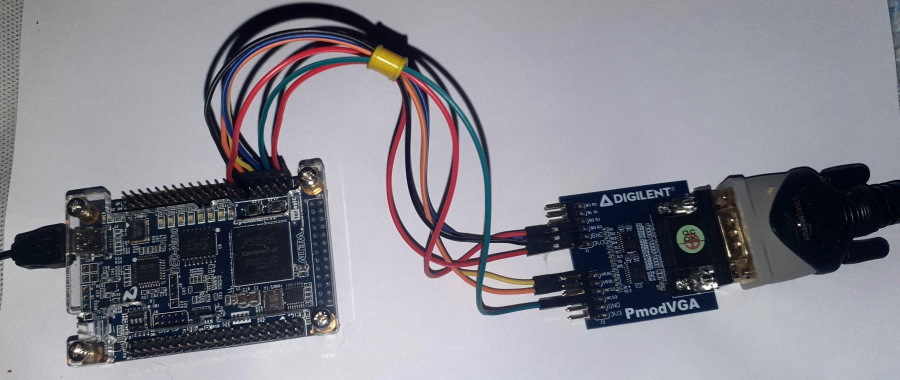

Kit FPGA Terasic DE0-nano et interface VGA

Objectifdécouvrir le protocole VGA et configurer la carte FPGA pour générer les signaux qui vont produire des images et autres animations vidéo à la résolution 640x480@60Hz.

Bonne lecture, et bonne rentrée à tous

Répondre avec citation

Répondre avec citation

pour cet article.

pour cet article.

:

:

Partager