En août dernier, Xilinx faisait la une des journaux (techniques, évidemment) avec son Virtex UltraScale+ VU19P, avec des spécifications alléchantes : 35 milliards de transistors, 9 millions d'éléments logiques, des transpondeurs pour une bande passante totale de 4,5 Tb/s. Intel ne pouvait que réagir, c'est maintenant chose faite : Stratix 10 GX 10M possède 10 millions d'éléments logiques, 43 milliards de transistors.

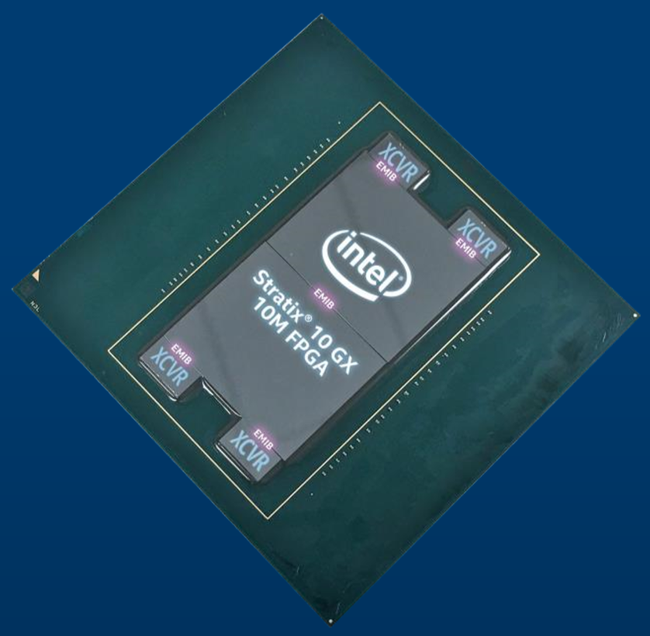

La différence avec les FPGA habituels est sa conception, à base de pucettes : un Stratix 10 GX 10M est constitué de deux pucettes qui fournissent les capacités du FPGA et de quatre transpondeurs. Les deux FPGA peuvent communiquer à l'aide de presque 26 000 connexions, pour un débit total de 6,5 To/s. Les six pucettes sont rassemblées à l'aide de la technologie EMIB, il s'agit d'ailleurs de sa première utilisation pour une puce complète aussi grande.

Ce nouveau FPGA est une grosse évolution par rapport à la génération précédente, le Stratix 10 2800 ne fournissant qu'un quart des éléments logiques et la moitié des broches de communication. Selon Intel, quatre Stratix 10 2800 consomment d'ailleurs 40 fois plus qu'un seul Stratix 10 GX 10M, à la même fréquence et à programme égal.

Pour le moment, Intel enchaîne les annonces en ce qui concerne ses FPGA : la gamme des Stratix 10 a débuté sa production en volume en 2017, puis plus rien jusqu'en septembre dernier. Là, le Stratix 10 DX a apporté un lien UPI (avec une cohérence entre caches), un port PCIe 4.0 et l'accès à de la mémoire persistante Optane, déjà grâce à assemblage de pucettes. Le Stratix 10 GX 10M est aussi un produit prévu de longue date et non l'assemblage rapide de deux FPGA plus petits : le Stratix 10 DX ne possède que trois millions d'éléments logiques, la pucette de base du Stratix 10 GX 10M en possède plus de cinq millions.

Source : Tom's Hardware

Répondre avec citation

Répondre avec citation

Partager