Bonjour a tous,

Je suis en train de modeliser un ADC en VHDL (LTC2255) et dans sa doc il est dit que la valeur des donnes en sortie est disponible 5 cycles d'horloge apres la valeur analogique echantillonnee. A cela s'ajoute aussi un temps de propagation, ce qui donne en clair:

data_out <= V_in after 5*Tclk+Tp

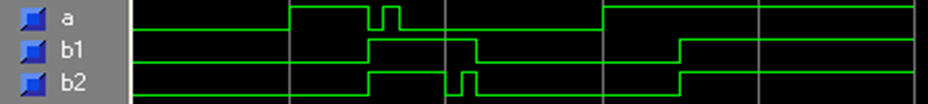

Avec Tclk =8ns et Tp= 5.4ns cela me donne un delai de 45.4ns. La simulation du composant (sans delai) donnait des resultats bons mais lorsque j'ai rajoute ce fameux delai je ne pouvais plus lire les donnees de sortie. En baissant ce delai a une valeur plus petite genre 10ns ca fonctionne de nouveau...

Pouvez-vous me dire d'ou ca peut venir? Et si il y a une autre methode pour rajouter un retard sur une sortie avec des resultats efficaces je suis preneur.

Merci

Répondre avec citation

Répondre avec citation

Partager