Bonjour,

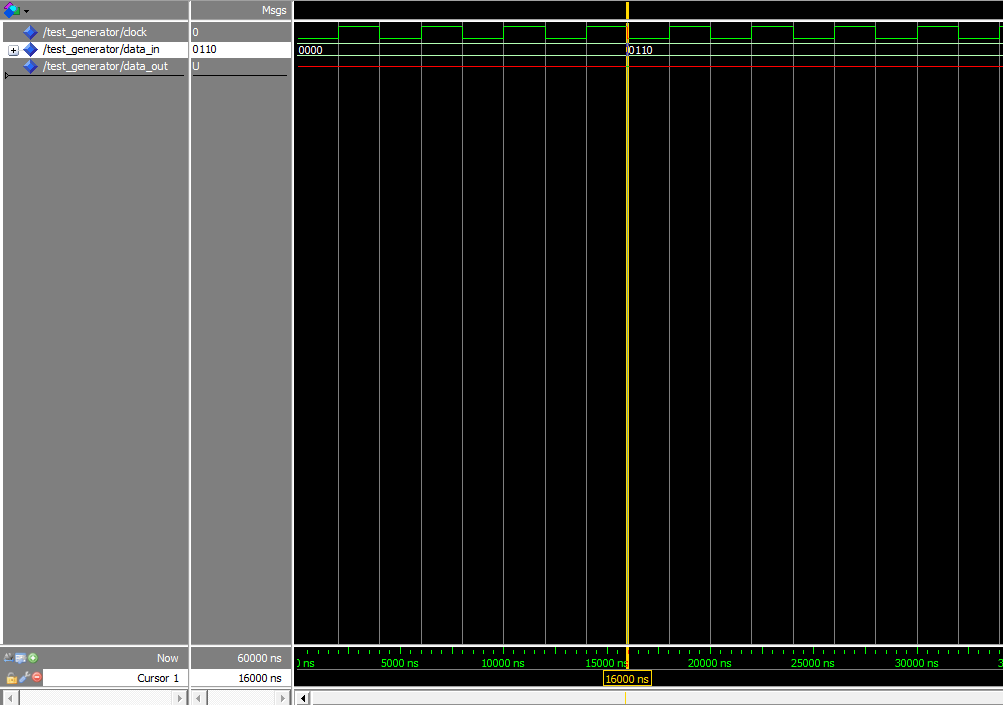

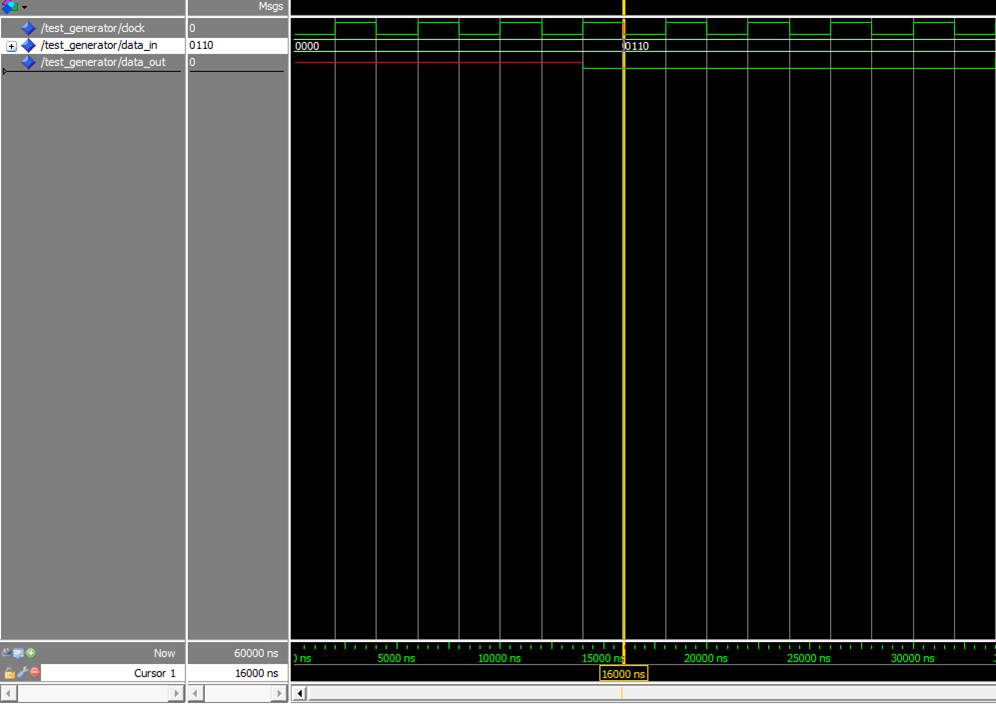

Je veux faire la description en VHDL générateur parallèle de 4 bits vers un bit série.

En effet, à chaque front dhorloge (250 kHz), nous prenons seulement un bit en commençant par le bit le moins significatif (LSB).

Exemple :

Entrée = "0101" (sur 4 bits)

Donc au premier front dhorloge, Sortie = '1' (LSB)

Deuxième front dhorloge, Sortie = '0'

Troisième front dhorloge, Sortie = '1'

Quatrième front dhorloge, Sortie = '0' (MSB)

Y a-t-il quelquun qui peut maider ?

Et merci

Répondre avec citation

Répondre avec citation

Partager