Bonjour a tous,

Je suis en train de me prendre la tete sur un truc qui peut paraitre simple a permiere vue mais l'approche du week end n'aide pas a ma concentration ^^

Voila j'ai cree plusieurs signaux en VHDL pour pouvoir les utiliser pour mes futurs testbench. J'ai donc cree un signal sinusoidal, carre, triangulaire , etc,...

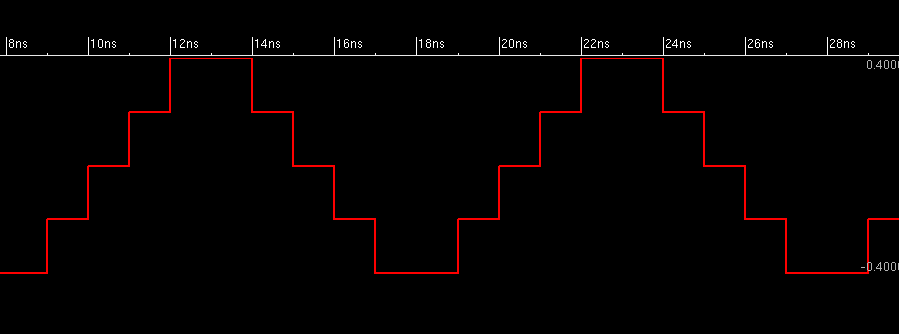

Mon probleme est le suivant, je n'arrive pas a avoir une resolution assez precise sur mes signaux, ou alors quand je change la resolution le signal n'a pas la bonne frequence. Je vous donne le code que j'ai ecrit pour un signal triangulaire et la courbe que j'obtiens en simulation lorsque je choisis comme frequence 100 000 000 Hz:

Code : Sélectionner tout - Visualiser dans une fenêtre à part

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

Pouvez-vous me dire ce que vous en pensez s'il vous plait ? Merci d'avance

Répondre avec citation

Répondre avec citation

Partager