Bonjour a tous!

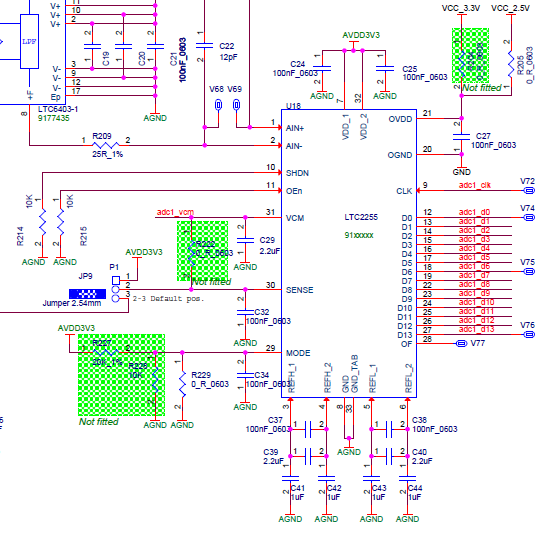

J'ai besoin de modeliser un can (dont la doc est donne en piece jointe) pour de la simulation seulement, c'est la premiere fois que je modelise un can et je galere un peu. Surtout que celui la me semble assez complexe...

Pouvez-vous me donner des conseils sur comment m'y prendre s'il vous plait. Et si vous savez ou je peux avoir des modeles de CAN dont je pourrais m'inspirer pour celui que je dois modeliser, ca serait bien aussi!.

Merci!

Répondre avec citation

Répondre avec citation

cela simplifie un peu ton entite et voila ce que j'ai:

cela simplifie un peu ton entite et voila ce que j'ai:

Partager