Bonjour,

je vais tenter d'exprimer clairement mon problème. Je désire réaliser un bus de com avec les E/S des cartes NI 9401 et ou 9403 que je possède sur mon cRIO, le tout programmé en FPGA, on risque d'aller un peu trop vite pour le processeur du cRIO et ça lui libère de la capacité de calcul.

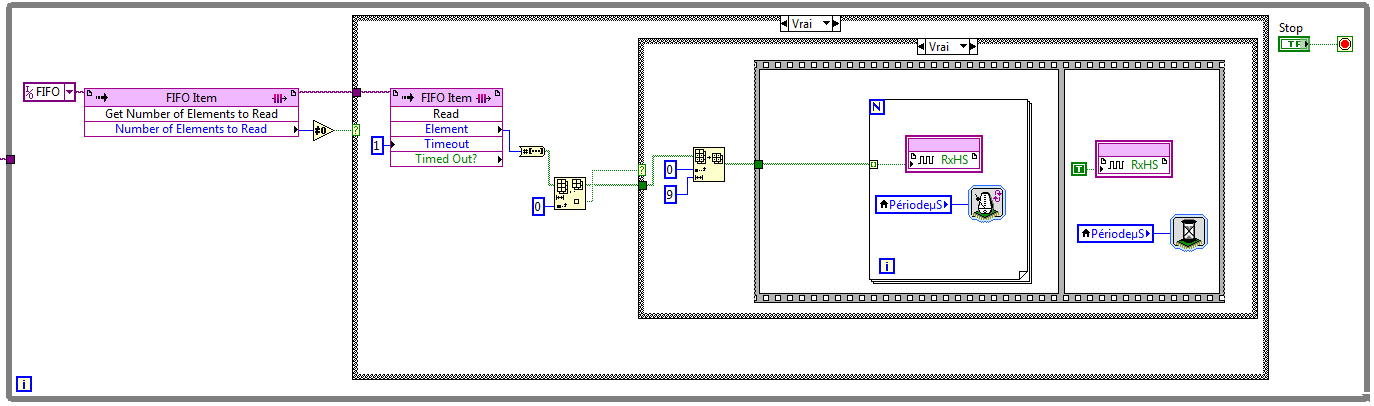

Du coup l'idée c'est d'envoyer à interval régulier (lorsque j'ai quelque chose à écrire sur l'E/S) des données (des 0 et/ou des 1). Je vous propose le code suivant :

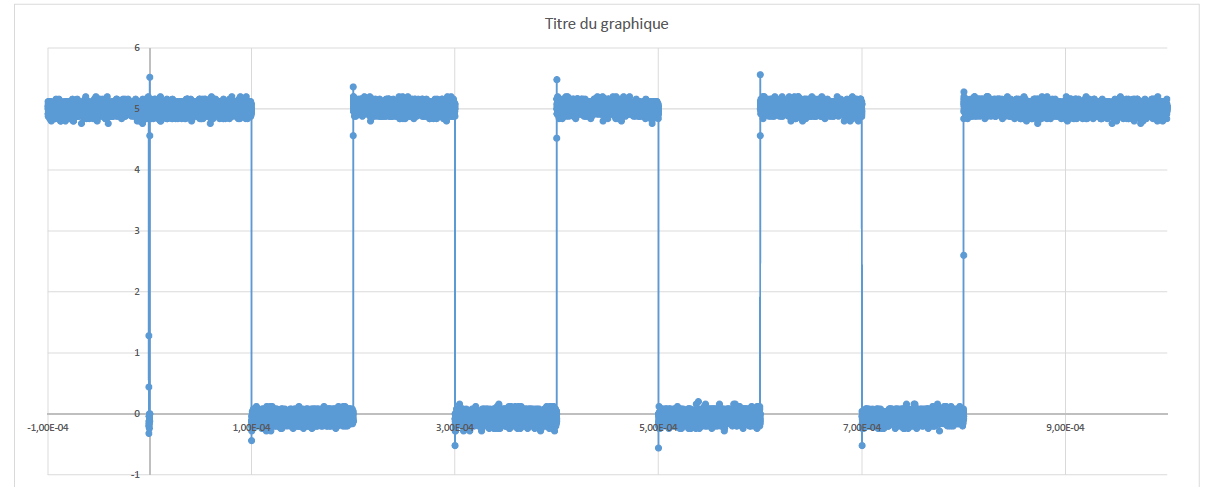

Voici ce que j'observe à l'osciloscope :

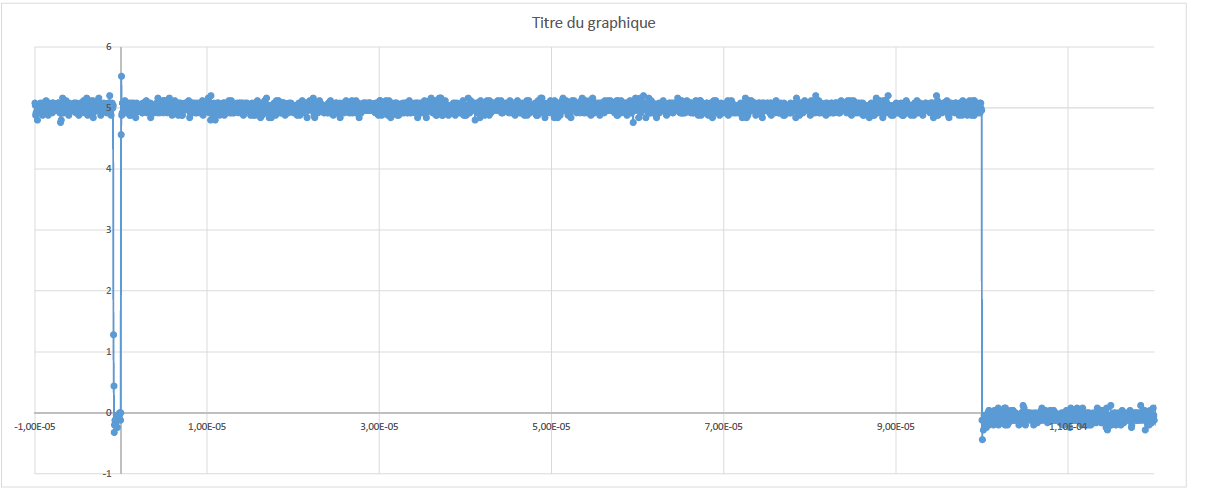

En zoumant :

La trame que je souhaite envoyé est la suivante : 010101010 après je mets mon bus à 1 le temps entre deux front devant être constant. Les 2 premires bits durent le temps d'1 c'est la mon problème. C'est la boucle fort qui "génère" mon signal et qui est cadencée ... D'où mon problème et mon interrogation. Qu'est ce que je fais de mal. Je respecte bien les bandes passante des deux cartes et le problème est le même avec les deux cartes. A chaque fois bien configurée en sortie.

Merci de votre coup de main !

Répondre avec citation

Répondre avec citation

Partager