Le marché des superordinateurs est en pleine évolution. Il y a peu, on ne parlait que dIntel et de ses Xeon. Puis sont venues les expériences avec ARM. AMD sest relancé dans la course avec ses Epyc. Maintenant, Tachyum vient annoncer ses processeurs Prodigy, pour donner un nouveau coup de fouet : soixante-quatre curs par puce (contre vingt-huit chez Intel, trente-deux chez AMD), huit canaux de mémoire (comme AMD, contre seulement six chez Intel). Ils ne sont pas encore prêts pour le déploiement on espère les voir sur le marché en 2020. Il nempêche quils ont de quoi surprendre : ils utilisent une conception radicalement différente, toutes les instructions étant forcément exécutées dans lordre dans lequel elles arrivent au processeur (alors quIntel et AMD les réordonnent pour utiliser au maximum tout le processeur, sans faire attendre certaines parties inutilement).

Les Prodigy disposent de leur propre jeu dinstructions, ce qui leur permet de faire table rase Intel étant poings et mains liées par la rétrocompatibilité, par exemple. Le compilateur doit être spécifiquement pensé pour larchitecture : si le processeur ne réordonne pas les instructions, cest parce quil attend que le compilateur sen charge. À cette fin, Tachyum a dabord développé un compilateur selon cette contrainte (un dérivé de GCC 7.2, pour le moment), puis seulement un processeur qui en bénéficie.

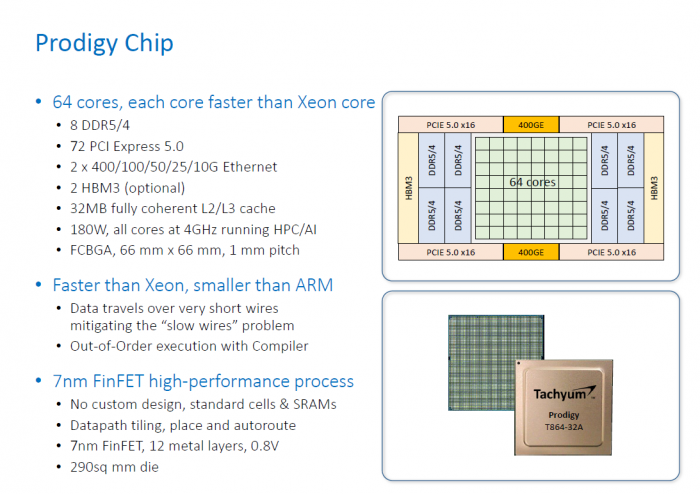

Cette conception permet de réduire lutilisation de transistors sur la puce chaque cur est ainsi beaucoup plus petit et peut être plus efficace (notamment parce que linformation a moins de distance à parcourir). Ainsi, sur moins de trois cents millimètres carrés (les Xeon montent jusque sept cents), Tachyum arrive à embarquer soixante-quatre curs, huit canaux de mémoire ECC (gérant la DDR4 et la DDR5), deux canaux supplémentaires pour de la mémoire à très haut débit HBM3, septante-deux canaux PCIe 5, deux ports Ethernet 400 Gb/s. En dautres termes, les entrées-sorties de ces processeurs sont hors normes ! Ils seront fabriqués par TSMC sur son processus à 7 nm.

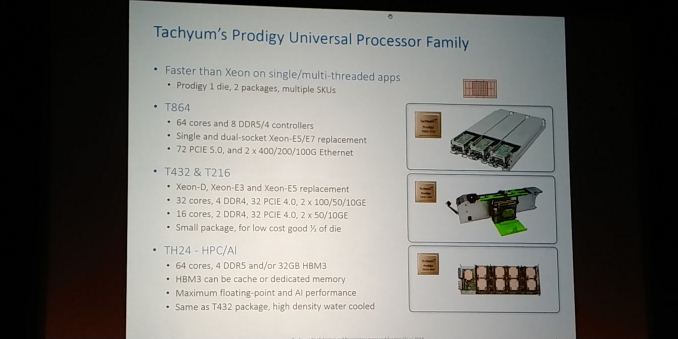

Plusieurs versions de ces puces sont prévues, en coupant les fonctionnalités non nécessaires selon les charges de travail à exécuter. Cela permet ainsi daugmenter la densité, donc de réduire les coûts pour les utilisateurs.

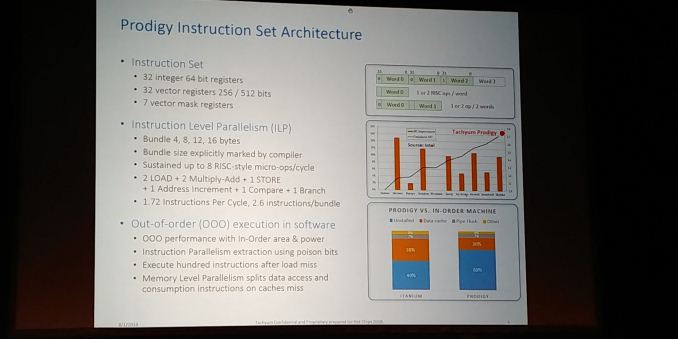

Larchitecture en elle-même nest pas très différente de ce qui se fait dans le reste de lindustrie. Chaque cur dispose de trente-deux registres de soixante-quatre bits pour des entiers, trente-deux registres vectoriels de deux cent cinquante-six ou cinq cent douze bits, sept registres de masques. À chaque coup dhorloge, un cur peut charger deux valeurs en mémoire, effectuer deux opérations de multiplication-addition, une écriture en mémoire, un incrément dadresse, un branchement. En moyenne, cela lui permet donc deffectuer 1,72 instruction huit microopérations par cycle.

Tout ceci nest possible que grâce aux annotations écrites par le compilateur, qui groupe explicitement des instructions par paquets de quatre à seize octets. Toute lexécution spéculative est aussi gérée par le compilateur, ce qui évite de perdre des transistors pour ce faire et de créer des failles, accessoirement.

Une autre idée derrière Prodigy est dexploiter le processeur à fond, tout le temps. Selon les simulations actuelles, un cur Prodigy passerait moins de vingt pour cent de son temps à attendre que des données à traiter arrivent (par rapport à la moitié du temps pour la défunte architecture Itanium dIntel, basée sur des principes similaires, où le compilateur devait effectuer une bonne partie du travail). De même, dans un centre informatique moderne, la plupart des processeurs sont rarement utilisés : un tiers du temps chez Amazon EC, quarante pour-cent du temps chez Facebook. Le reste du temps, les processeurs consomment, mais neffectuent aucun calcul, alors quils pourraient être utilisés pour des tâches dapprentissage automatique.

Sources : Kleiner Supercomputer-Chip soll Intels Xeons schlagen, Hot Chips 2018: Tachyum Prodigy CPU Live Blog.

Répondre avec citation

Répondre avec citation

: un processeur c'est con comme une b*te

: un processeur c'est con comme une b*te  )

) Consultez nos FAQ :

Consultez nos FAQ :

Partager