Bonjour, j'ai un problème que je ne comprend pas, j'essaie de décrire en comportemental un décodeur 2 vers 4, qui a donc deux entrées (E1 et E0) et quatre sorties (S3, S2, S1 et S0).

Pour déterminer les sorties dans le process, je convertis la concaténation de E1 et E0 en entier et je fais un CASE pour exprimer les sorties.

J'ai donc fais ça :

Et là il n'y a pas de problèmes, ça fonctionne :

Code : Sélectionner tout - Visualiser dans une fenêtre à part

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

Maintenant j'ai voulu mettre le signal de sortie dans un signal intermédiaire et connecter ce signal aux vraies sorties seulement à la fin du process :

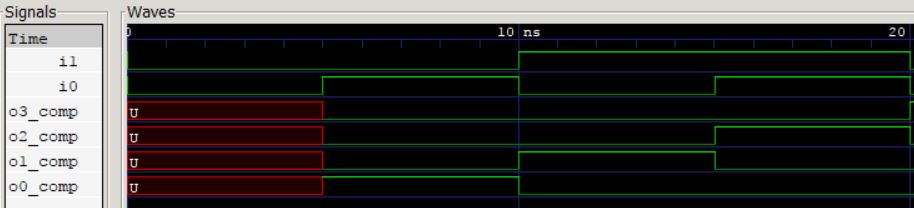

Et là voilà ce que j'obtiens :

Code : Sélectionner tout - Visualiser dans une fenêtre à part

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

Pourquoi il me dit que le signal est undefined ? C'est comme si tout était décalé, je comprends pas...

Répondre avec citation

Répondre avec citation

Partager