Pour ceux que cela étonne je sais sûrement tout ce qui sera dit mais j'aimerais des confirmations (qui sait j'ai peut être loupé un truc dans l'explication théorique).

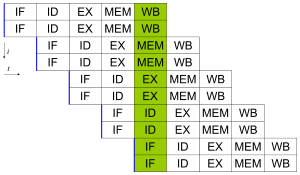

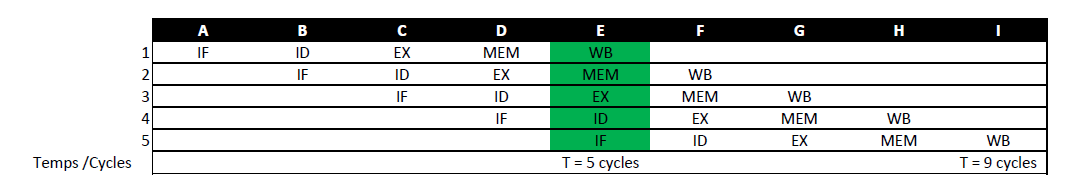

Alors première question le superscalaire c'est toujours par bloc de 2 instructions non ?

Pour out of order , in-order , on gros en out of order(instruction dans le désordre) c'est pour en gros évité le pipeline stall ?

En faite je me suis posé c'est question a cause de la prog PS2 et du code asm fourni :

-j'ai pas regardé en détails , mais j'ai pas l'impression que le compilo fait attention que le proc soit superscalaire (en gros par bloc de 2 instructions).

-le code devrait prendre en compte la pipeline , la aussi a première vu il met le code bien dans l'ordre (et si vous avez deja optimisé un proc avec pipeline vous les mettez pas forcément dans lordre pour éviter les stall).

-sur un x86 , la pipeline n'est pas forcément pris en compte (de je que je vois la aussi avec le compilo) donc sur un compilo GCC x86 cela veut dire sûrement qu'il suppose que mon CPU est en OoO (out of order) ?

Merci les copains ! (je pense que tout ceux qui posteront je les connais).

Répondre avec citation

Répondre avec citation

Consultez nos FAQ :

Consultez nos FAQ :

Partager