par , 19/08/2022 à 08h00 (3116 Affichages)

Dans un flux de données binaire tel que 1 0 0 1 1 0 ... , détecter une séquence particulière est un exercice de logique séquentielle que lon peut résoudre grâce à une approche par machine à états finis (Finite State Machine FSM).

Par exemple, la machine à états finis du graphe ci-dessous permet de détecter la séquence 1 1 0 1 :

S0, S1, S1 et S3 sont les états de la machine, et les étiquettes au niveau des arcs orientés définissent les transitions (les conditions de passage dun état à un autre) et létat de la sortie. Létiquette de chaque transition est un couple état entrée/état sortie.

Par exemple, (S0)---1/0--->(S1) signifie que létat passe de S0 à S1 si lentrée (le bit courant du flux) est égale à 1, et dans ce cas la sortie passe à 0. Pour une description complète, chaque état (Si) a forcément deux arcs qui partent : un pour lentrée égale à 0, un autre pour lentrée égale à 1.

Dans une détection de séquence, on veut naturellement que la sortie passe à 1 si la bonne séquence 1 1 0 1 est détectée, ici sur larc (S3)---1/1--->(S0).

Remarquez que la machine décrite nautorise pas de chevauchement dans la séquence. Par exemple dans le flux 1 1 0 1 1 0 1, on pourrait voir la séquence apparaître deux fois :

- 1 1 0 1 1 0 1

- 1 1 0 1 1 0 1

Mais dans ce cas, le 1 en 4e position chevaucherait les deux séquences, ce qui nest pas autorisé daprès le graphe. Seule la 1re séquence sera détectée par notre machine.

Cette description de machine à états finis où la sortie dépend à la fois de létat courant (Si) et de lentrée constitue une machine de Mealy.

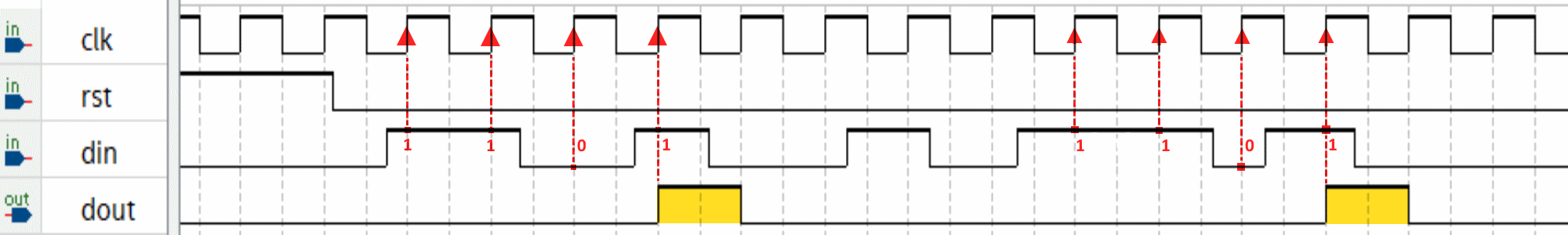

Voici un exemple de détection obtenu en simulation :

Simulation : la séquence 1 1 0 1 est détectée deux fois

Simulation : la séquence 1 1 0 1 est détectée deux fois

Lentrée din est asynchrone mais la lecture du flux en entrée, la détection et les transitions opèrent sur front montant de lhorloge.

En logique séquentielle, le traitement seffectue avec trois processus :

- un processus combinatoire qui calcule létat futur à partir de lentrée et de létat présent ;

- un processus séquentiel où létat présent est mis à jour par létat futur et mémorisé sur front montant de lhorloge (ou remis à létat initial (S0) sur un signal Reset asynchrone) ;

- un processus combinatoire qui calcule la sortie à partir de lentrée et de létat présent.

Voici le module complet de détection de la séquence en Verilog avec les trois processus :

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

| module top(clk, rst, din, dout); // détection de séquence 1101

input clk, rst, din;

output reg dout;

localparam S0 = 2'b00,

S1 = 2'b01,

S2 = 2'b10,

S3 = 2'b11;

(* syn_encoding = "user" *) reg [1:0] state;

reg [1:0] state_next;

/* Mise à jour de létat présent par létat futur sur les fronts montant

dhorloge (reset asynchrone inclus) */

always @(posedge clk or posedge rst) begin

if (rst)

state <= S0;

else

state <= state_next;

end

/* Calcul des sorties à partir de l'entrée et de létat présent */

always @(posedge clk or posedge rst) begin

if (rst)

dout <= 1'b0;

else

dout <= (state == S3) && din; // sortie dépend de l'entrée et de l'état

end

/* Calcul de létat futur à partir de l'entrée et de létat présent */

always @(*) begin

case (state) // selon l'état présent

S0 : state_next <= din ? S1 : S0;

S1 : state_next <= din ? S2 : S0;

S2 : state_next <= din ? S2 : S3;

S3 : state_next <= S0;

endcase

end

endmodule |

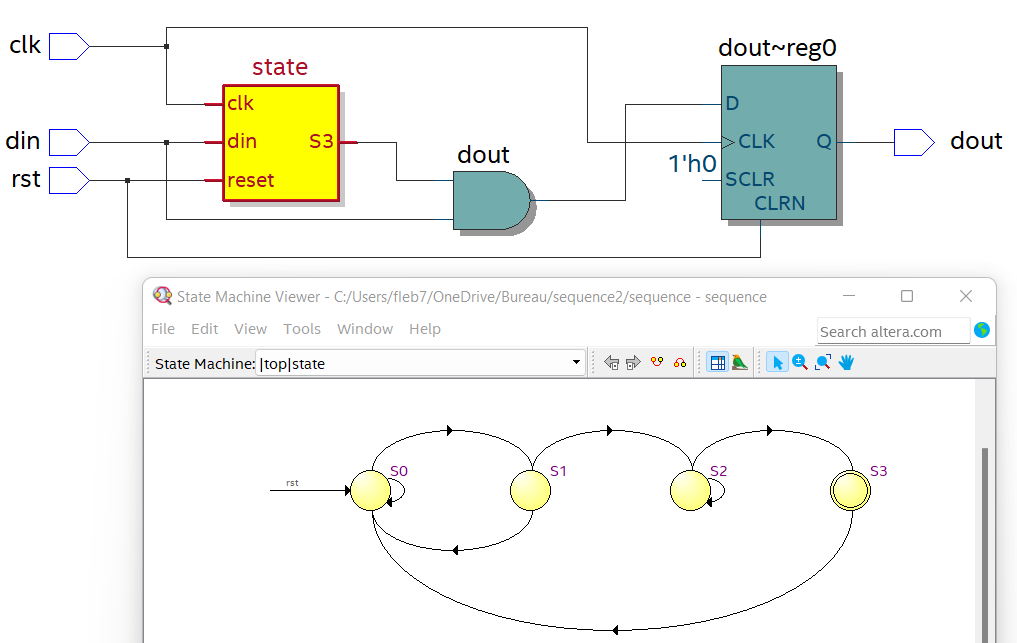

Le système analysé est bien une machine à états finis

Le système analysé est bien une machine à états finis

Vous noterez lattribut syn_encoding redéfini à "user" pour lencodage des états :

(* syn_encoding = "user" *) reg [1:0] state;

Voir Intel® Quartus® Prime Pro Edition Help version 22.2 - syn_encoding Verilog HDL Synthesis Attribute.

Sans cette redéfinition, Quartus superpose à lencodage des états défini par lutilisateur un autre encodage par défaut (dautres encodages sont possibles : one-hot, Gray, etc. Chacun pour éviter des états transitoires indésirables). Jai fait cela pour que Quartus laisse tels quels mes états définis sur 2 bits dans le code à la synthèse du projet :

1

2

3

4

| localparam S0 = 2'b00,

S1 = 2'b01,

S2 = 2'b10,

S3 = 2'b11; |

Et jai pu ainsi comparer le circuit synthétisé avec celui issu de mes calculs établis sur les tables de vérité écrites « à la main »

Eh bien le synthétiseur est au moins aussi fort que moi (certes, il est quand même bien plus rapide). Ce nest pas que je navais pas confiance, mais jaime bien me rendre compte par moi-même pour comprendre

(certes, il est quand même bien plus rapide). Ce nest pas que je navais pas confiance, mais jaime bien me rendre compte par moi-même pour comprendre

Regardez le circuit synthétisé ci-dessous :

Les blocs state~4 et state~5 sont les bascules qui mémorisent respectivement le bit de poids faible et le bit de poids fort de létat (Si). Les blocs state~6 et state~7 sont les blocs de logique combinatoire qui calculent létat suivant en fonction de létat présent et de lentrée din.

Le schéma nest pas facile à suivre, mais jai fait apparaître à gauche le détail du bloc state~7. Sur le papier, javais oublié la simplification de léquation qui amène une porte XOR. Le synthétiseur ne la pas loupée, lui ! Je valide le circuit généré...

(certes, il est quand même bien plus rapide). Ce nest pas que je navais pas confiance, mais jaime bien me rendre compte par moi-même pour comprendre

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter une séquence » dans le blog Viadeo](https://forum.developpez.be/images/misc/bookmarksite_viadeo.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter une séquence » dans le blog Twitter](https://forum.developpez.be/images/misc/bookmarksite_twitter.png)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter une séquence » dans le blog Google](https://forum.developpez.be/images/misc/bookmarksite_google.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter une séquence » dans le blog Facebook](https://forum.developpez.be/images/misc/bookmarksite_facebook.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter une séquence » dans le blog Digg](https://forum.developpez.be/images/misc/bookmarksite_digg.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter une séquence » dans le blog Delicious](https://forum.developpez.be/images/misc/bookmarksite_delicious.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter une séquence » dans le blog MySpace](https://forum.developpez.be/images/misc/bookmarksite_myspace.gif)

![Envoyer le billet « [FPGA] Créer un circuit logique pour détecter une séquence » dans le blog Yahoo](https://forum.developpez.be/images/misc/bookmarksite_yahoo.gif)