# **USB Bridge Controller CH341**

DataSheet Version: 3C http://wch.cn

## 1. Introduction

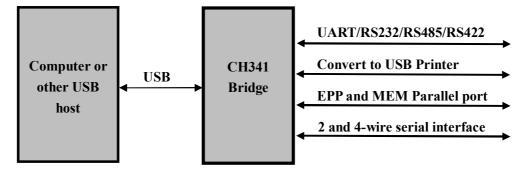

CH341 is a USB converter chip, which converts USB to serial UART interface, printer interface, parallel port interface, and common 2/4-wire synchronize serial communication interfaces etc.

In UART mode, CH341 provides UART transmit enable, UART receive ready rate control signals ,etc., and common MODEM interface signals, to expand UART interface of computer or upgrade common serial interface devices to USB directly.

In print port mode, CH341 provides a standard USB print port compatible with USB-related specifications and the Windows operating system for upgrading a print port printer directly to the USB.

In parallel port mode, CH341 provides an 8-bit parallel interface in EPP mode or MEM mode for input and output data directly without a microcontroller/DSP/MCU.

In addition, CH341B/F/A support commonly used synchronous serial interface such as 2-wire interface (SCL line, SDA line) and 4-wire interface (CS line, SCK/CLK line, MISO/SDI/DIN Line, MOSI/SDO/DOUT line), etc.

### 2. Features

#### **2.1. Introduction**

- Full speed USB device interface, USB 2.0 compatible.

- Supports 5V and 3.3V power supply.

- Optional: customize the vendor ID, product ID, serial number, etc. via an external low-cost serial EEPROM.

- Low cost, convert the original serial port peripheral devices, the original print port printer, and the original parallel port peripheral devices to USB directly.

- RoHS compliant SOP-28, SSOP-20 and QFN28 lead-free package.

- Only compatible with the applications, and cannot be absolutely the same.

### 2.2. UART

- Emulate standard UART interface, used to upgrade the original serial devices or expand additional UART via USB.

- Original UART applications are totally compatible without any modification.

- Hardware full duplex serial UART interface, integrated transmit-receive buffer, supports communication baudrates varies from 50bps to 2Mbps.

- Supports 5, 6, 7 or 8 data bits and 1 or 2 stop bits, supports odd, even, none, mark, space parity.

- Supports UART transmit enable, UART receive ready rate control signals and so on, and common MODEM interface signals.

- Provides further RS232, RS485, RS422 interface, etc. through external voltage conversion chip.

- Supports access to the CH341 external serial EEPROM memory in UART communication.

#### 2.3. Print Port

- Standard USB print port for upgrading the original print port printer, compatible with the relevant USB specifications.

- Compatible with Windows/Linux/MACOS and so on, and the application is fully compatible.

- Supports various standard print port printers, optional low speed printing and high speed printing.

- Supports two-way communication of the IEEE-1284 specification and supports one-way and two-way transmission of printers.

#### 2.4. Parallel Port

- Two modes are available: EPP mode and MEM mode.

- EPP provides signals such as AS#, DS# and WR# etc. Similar to EPP V1.7 or EPP V1.9.

- The MEM mode provides signals such as A0, RD# and WR# etc. Which is similar to the memory read/write mode.

#### 2.5. Synchronous serial port

- FlexWire<sup>TM</sup> technology, enables flexible 2-wire to 5-wire synchronous serial ports through software.

- As a Host/Master host, it supports common synchronous serial interfaces such as 2-wire and 4-wire.

- The 2-wire interface provides two signal lines SCL and SDA, and supports 4 transmission speeds.

## 3. Packages

| Package   | Width Of Plastic |        | Pitch Of Pin |         | Instruction Of Package            | Ordering<br>Information |

|-----------|------------------|--------|--------------|---------|-----------------------------------|-------------------------|

| SOP-28    | 7.62mm           | 300mil | 1.27mm       | 50mil   | Small outline 28-pin patch        | CH341B                  |

| SOP-28    | 7.62mm           | 300mil | 1.27mm       | 50mil   | Small outline 28-pin patch        | CH341A                  |

| QFN28_4X4 | 4*4mm            |        | 0.4mm        | 15.7mil | Square lead free 28-pin           | CH341F                  |

| SSOP-20   | 5.30mm           | 209mil | 0.65mm       | 25mil   | Shrink Small outline 20-pin patch | CH341C                  |

| SSOP-20   | 5.30mm           | 209mil | 0.65mm       | 25mil   | Shrink Small outline 20-pin patch | СН341Т                  |

| SSOP-20 5. | .30mm | 209mil | 0.65mm | 25mil | Shrink Small outline 20-pin patch | CH341H |

|------------|-------|--------|--------|-------|-----------------------------------|--------|

|------------|-------|--------|--------|-------|-----------------------------------|--------|

Note:

CH341C/T is only used for USB to serial port or USB to 2-wire interface.

CH341H is only used for USB to 4-wire interface, etc. (such as SPI). New designs are not recommended. CH341B or CH341F is recommended.

CH341A, CH341T and CH341H must be connected with crystal and oscillation capacitor.

CH341B, CH341F and CH341C can choose to connect external crystal and capacitor, or choose not to connect externally and directly use the built-in clock.

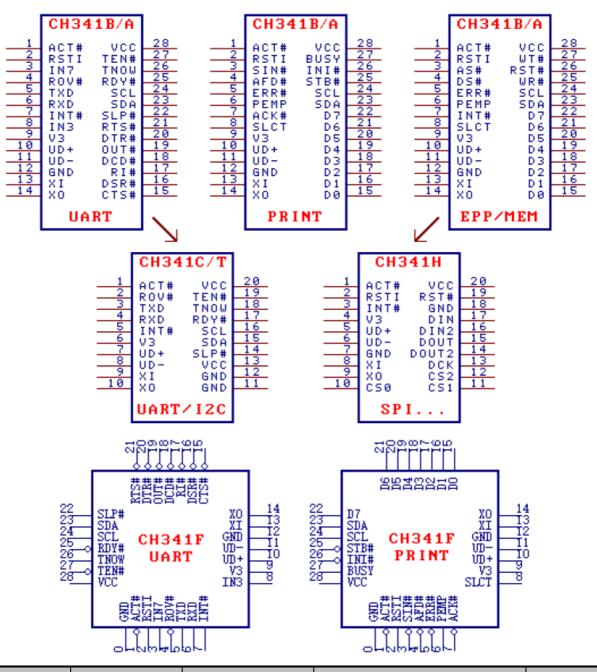

## 4. Pin Out

#### 4.1 General description

The specific function of CH341 is determined by the function configuration after reset, the definition of the same pin may be different under different functions.

CH341C/T and CH341H adopt SSOP-20 package, which is the simplified version of CH341B/A/F. The pins with the same name of the three have the same function. Multiple VCC pins of CH341C/T and CH341H are connected in parallel as VCC, and multiple GND pins are connected in parallel as GND.

#### 4.2 Standard common pin

|          | Pin<br>Number |       | Pin Name | Туре       | Pin Description                                                                                                                                                                                               |

|----------|---------------|-------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 341B/A/F | 341C/T        | 341H  |          |            |                                                                                                                                                                                                               |

| 28       | 20, 13        | 20    | VCC      | POWER      | The positive power input terminal requires<br>an external 0.1uF power decoupling<br>capacitor                                                                                                                 |

| 12,0     | 11, 12        | 7, 18 | GND      | POWER      | Common ground terminal, directly<br>connected to the ground wire of the USB<br>bus                                                                                                                            |

| 9        | 6             | 4     | V3       | POWER      | When the power supply voltage is 3.3V, connect VCC to input the external power supply, when the power supply voltage is 5V, the external capacity is $0.01 \text{uF} \sim 0.1 \text{uF}$ decoupling capacitor |

| 13       | 9             | 8     | XI       | IN         | The input terminal of the crystal oscillator<br>requires an external crystal and oscillation<br>capacitor.<br>For the built-in clock mode of<br>CH341B/F/C, XI should be connected to<br>GND                  |

| 14       | 10            | 9     | XO       | OUT        | The inverting output terminal of the crystal<br>oscillator requires an external crystal and<br>oscillation capacitor.<br>For the built-in clock mode of<br>CH341B/F/C, XO should be left floating             |

| 10       | 7             | 5     | UD+      | USB signal | Connect to USB D+ Signal directly                                                                                                                                                                             |

| 11 | 8    | 6    | UD-  | USB signal                        | Connect to USB D-Signal directly                                                                                                                |

|----|------|------|------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 1    | 1    | ACT# | OUT                               | USB device configuration completed status output, low-level active                                                                              |

| 2  | NONE | 2    | RSTI | IN                                | External reset input, active high, built-in pull-down resistor                                                                                  |

| 24 | 16   | NONE | SCL  | Open drain<br>output              | Chip function configuration output, built-in<br>pull-up resistor, can be connected to the<br>SCL pin of the serial EEPROM<br>configuration chip |

| 23 | 15   | NONE | SDA  | Open drain<br>output and<br>input | Chip function configuration input, built-in<br>pull-up resistor, can be connected to the<br>SDA pin of the serial EEPROM<br>configuration chip  |

## 4.3 Asynchronous serial port mode pin

| Pin<br>Number |        | Pin Name | Туре         | Pin Description                                                              |  |

|---------------|--------|----------|--------------|------------------------------------------------------------------------------|--|

| 341B/A/F      | 341C/T |          |              |                                                                              |  |

| 5             | 3      | TXD      | OUT          | Serial data output                                                           |  |

| 6             | 4      | RXD      | IN           | Serial data input, built-in pull-up resistor                                 |  |

| 27            | 19     | TEN#     | IN           | Serial port transmission enable, active low, built-in pull-up resistor       |  |

| 25            | 17     | RDY#     | OUT          | The serial port is ready for reception, active low                           |  |

| 26            | 18     | TNOW     | OUT          | The serial port sends the status indication in progress, active high         |  |

| 4             | 2      | ROV#     | OUT tristate | Serial receiving buffer overflow, low level is effective                     |  |

| 15            | NONE   | CTS#     | IN           | MODEM contact input signal, clear to send, low effective                     |  |

| 16            | NONE   | DSR#     | IN           | MODEM contact input signal, data device is ready, low effective              |  |

| 17            | NONE   | RI#      | IN           | MODEM contact input signal, ringing indicator, low effective                 |  |

| 18            | NONE   | DCD#     | IN           | MODEM contact input signal, carrier detection, low effective                 |  |

| 20            | NONE   | DTR#     | OUT tristate | MODEM contact output signal, data terminal is ready, low effective           |  |

| 21            | NONE   | RTS#     | OUT tristate | MODEM contact output signal, request to send, low effective                  |  |

| 19            | NONE   | OUT#     | OUT tristate | User-defined general output signal, low-level effective                      |  |

| 7             | 5      | INT#     | IN           | Custom interrupt request, valid on rising edge,<br>built-in pull-up resistor |  |

| 8  | NONE | IN3  | IN           | User-defined universal input signal, it is recommended not to use |

|----|------|------|--------------|-------------------------------------------------------------------|

| 3  | NONE | IN7  | IN           | User-defined universal input signal, it is recommended not to use |

| 22 | 14   | SLP# | OUT tristate | Sleep state output signal, active low                             |

## 4.4 Print port mode pin

| 341B/A/F<br>Pin Number | Pin Name | Туре         | Pin Description                                                                             |

|------------------------|----------|--------------|---------------------------------------------------------------------------------------------|

| 22~15                  | D7~D0    | OUT tristate | 8-bit parallel data output, connect to DATA7 $\sim$ DATA0                                   |

| 25                     | STB#     | OUT          | Data strobe output, active low, connect to STROBE                                           |

| 4                      | AFD#     | OUT          | Automatic line feed output, active low, connect to AUTO-FEED                                |

| 26                     | INI#     | OUT          | Initialize the printer, active low, connect to INIT                                         |

| 3                      | SIN#     | OUT tristate | Select printer, low level is active, connect to SELECT-IN                                   |

| 5                      | ERR#     | IN           | Printer error, low active, built-in pull up, connect to ERROR or FAULT                      |

| 8                      | SLCT     | IN           | Printer online, high efficiency, built-in pull-up,<br>connect to SELECT or SLCT             |

| 6                      | PEMP     | IN           | The printer is out of paper, high efficiency, built-in pull-up, connect to PEMPTY or PERROR |

| 7                      | ACK#     | IN           | Printer data receiving response, valid at rising edge,<br>built-in pull-up, then ACK        |

| 27                     | BUSY     | IN           | Printer is busy, high effective, built-in pull-up, connect to BUSY                          |

## 4.5 Parallel mode pin

| 341B/A/F<br>Pin Number | Pin Name | Туре            | Pin Description                                                         |

|------------------------|----------|-----------------|-------------------------------------------------------------------------|

| 22~15                  | D7~D0    | IN/OUT tristate | 8-bit bidirectional data bus with built-in pull-up resistor             |

| 25                     | WR#      | OUT             | EPP mode: write operation instruction, low level write, high level read |

|                        |          |                 | MEM mode: write strobe output WR#, active low                           |

| 4                      | DS#      | OUT             | EPP mode: data operation strobe, active low                             |

| 4                      | D8#      | OUT             | MEM mode: read strobe output RD#, active low                            |

| 26                     | RST#     | OUT             | Reset output, active low                                                |

| 2  |       |              | EPP mode: address operation strobe, active low                        |

|----|-------|--------------|-----------------------------------------------------------------------|

| 3  | AS#   | OUT tristate | MEM mode: address line output ADDR or A0                              |

| 27 | WAIT# | IN           | For CH341B/F/A chip: request to wait, low active, built-in pull-up    |

| 7  | INT#  | IN           | Interrupt request input, rising edge valid, built-in pull-up resistor |

| 5  | ERR#  | IN           | Custom general-purpose input, built-in pull-up resistor               |

| 8  | SLCT  | IN           | Custom general-purpose input, built-in pull-up resistor               |

| 6  | PEMP  | IN           | Custom general-purpose input, built-in pull-up resistor               |

## 4.6 Synchronous serial port mode pin

| Pin<br>Number |       | Pin Name Type |                                | Pin Description                                                        |  |

|---------------|-------|---------------|--------------------------------|------------------------------------------------------------------------|--|

| 341B/A/F      | 341H  |               |                                |                                                                        |  |

| 22            | 17    | DIN           | IN                             | 4-wire serial data input, alias MISO or SDI, built-in pull-up resistor |  |

| 21            | 16    | DIN2          | IN                             | 5-wire serial data input 2, built-in pull-up resistor                  |  |

| 20            | 15    | DOUT          | OUT tristate                   | 4-wire serial data output, alias MOSI or SDO                           |  |

| 19            | 14    | DOUT2         | OUT tristate                   | 5-wire serial data output 2                                            |  |

| 18            | 13    | DCK           | OUT tristate                   | 4-wire/5-wire serial port clock output, alias SCK                      |  |

| 17~15         | 12~10 | CS2~CS0       | OUT tristate                   | 4-wire serial chip select output $2\# \sim 0\#$                        |  |

| 24            | NONE  | SCL           | Open drain output              | Clock output of 2-wire serial port, built-in pull-up resistor          |  |

| 23            | NONE  | SDA           | Open drain output<br>and input | Data input and output of 2-wire serial port, built-in pull-up resistor |  |

| 26            | 19    | RST#          | OUT                            | Reset output, active low                                               |  |

| 7             | 3     | INT#          | IN                             | Interrupt request input, rising edge valid, built-in pull-up resistor  |  |

| 5, 8, 6       | NONE  |               | IN                             | Custom general-purpose input, built-in pull-up resistor                |  |

# **5. Function Description**

#### 5.1 General description

For the data in this manual, the suffix B is a binary number, and the suffix H is a hexadecimal number, otherwise it is a decimal number.

CH341 is a USB bus adapter chip, providing asynchronous serial port, standard USB printer port, parallel port and synchronous serial interface. This manual mainly provides the description of asynchronous serial port and printer port. For the description of parallel port and synchronous serial interface, please refer to manual (2).

#### 5.2 Hardware description

Some pins of the CH341 chip have multiple functions, so they have different characteristics during the reset period and the normal working state after the reset is completed. All three-state output pins have built-in pull-up resistors, which are used as output pins after the chip reset is completed and the firmware is executed. During the chip reset, the three-state output is disabled, and the built-in pull-up resistor provides pull-up current . If necessary, the external circuit can provide an external pull-up resistor or pull-down resistor in the circuit to set the default level of the relevant pin during the reset period of the CH341 chip. The resistance of the external pull-up resistor or pull-down resistor is usually Between  $2K\Omega \sim 5K\Omega$ . For example, the AS# in parallel mode is forbidden to output tri-state during chip reset, and only the pull-up current is maintained at a high level. In order to prevent the external circuit from being interfered and malfunctioning during this period, a pull-up resistor of  $3K\Omega$  can be added. , In order to maintain a more stable high level.

The ACT# pin of CH341 is used to output the status of USB device configuration completion. When the USB device has not been configured or is unconfigured, this pin outputs a high level. When the USB device is configured, this pin outputs a low level. The ACT# pin can be connected to an external light-emitting diode LED with a current-limiting resistor to indicate the completion status of the USB device configuration.

The CH341 chip has a built-in USB pull-up resistor, and the UD+ and UD- pins should be directly connected to the USB bus.

The CH341 chip has a built-in power-on reset circuit. The RSTI pin of CH341 is used to input an asynchronous reset signal from the outside; when the RSTI pin is high, the CH341 chip is reset; when the RSTI pin returns to low, CH341 will continue to delay reset about 20mS, and then enter Work status. In order to reliably reset during power-up and reduce external interference, a capacitor with a capacitance of about 0.1uF can be connected between RSTI pin and VCC.

When CH341A/T/H chip works normally, it needs to provide 12MHz clock signal to XI pin from outside. Generally, the clock signal is generated by the built-in inverter of CH341 through crystal stable frequency oscillation. The peripheral circuit only needs to connect a 12MHz crystal between the XI and XO pins, and connect the XI and XO pins to the ground respectively with an oscillation capacitor.

CH341B/F/C chip supports two modes: external clock and built-in clock. For external clock mode, refer to the above-mentioned CH341A external 12MHz crystal and capacitor; built-in clock mode should connect XI pin to GND and leave XO pin open to save external crystal And the oscillation capacitor.

CH341 chip supports 5V power supply voltage or 3.3V power supply voltage. When using a 5V working voltage, the VCC pin of CH341 chip inputs an external 5V power supply, and the V3 pin should be externally connected with a power decoupling capacitor with a capacity of  $0.01 \text{ uF} \sim 0.1 \text{ uF}$ . When using 3.3V operating voltage, the V3 pin of the CH341 chip should be connected to the VCC pin, and an external 3.3V power supply should be input at the same time, and the operating voltage of other circuits connected to the CH341 chip cannot exceed 3.3V

#### **5.3 Function configuration**

CH341 uses SCL and SDA pins to configure the functions of the chip. There are two ways: direct combination configuration and external chip configuration.

Direct combination configuration is to connect and combine SCL pin and SDA pin to configure the function of CH341. Its characteristic is: no additional cost, but only the default manufacturer ID and product ID and other information can be used. In the direct combination configuration mode, except for the product ID, other information is the same as the default value of the external chip configuration. CH341H chip has connected SDA to low level internally.

| ľ   | SCL and SDA pin status | Chip function | Default product ID |  |

|-----|------------------------|---------------|--------------------|--|

| - 1 |                        |               |                    |  |

The external chip configuration is a two-wire synchronous serial port composed of SCL and SDA pins, connected to an external serial EEPROM configuration chip, and the chip function, manufacturer ID, product ID, etc. are defined through the EEPROM chip. The configuration chip should use the 24CXX series chip with 7-bit address, for example: 24C01A, 24C02, 24C04, 24C16, etc. Its characteristic is: It can flexibly define chip functions and various common identification information of USB products. Through the tool software CH341CFG.EXE under Windows, the data in the serial EEPROM can be modified online at any time, and the chip function and various identification information of CH341 can be redefined.

Generally, after reset, the CH341 chip's built-in firmware first checks the content of the external configuration chip through the SCL and SDA pins. If the content is invalid, use direct combination configuration according to the state of SCL and SDA. In order to avoid the use of SCL and SDA in the above configuration process to affect the 2-wire synchronous serial port, the ACT# pin of CH341 can be set to low level through a  $2K\Omega$  resistor during the configuration process, then CH341 will be forcibly configured as EPP/MEM parallel port and synchronous serial port, Instead of actively checking the external configuration chip.

CH341B, CH341F and CH341C chips support batch function program customization and batch preset product ID.

| Byte Address | Abbreviation | Description                                                                                                                                                                              | Default    |

|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 00H          | SIG          | external configuration information valid reg, must be 53H.<br>Invalid for other value, Use direct combination<br>configuration                                                           | 53H        |

| 01H          | MODE         | Select the communication interface: 23H=serial port,<br>12H=print port or parallel port, other values will invalidate<br>the configuration data, use direct combination<br>configuration | 23H or 12H |

| 02H          | CFG          | For the specific configuration of the chip, refer to the table<br>below for bitwise description                                                                                          | FEH        |

| 03H          |              | (Reserved unit, must be 00H or 0FFH)                                                                                                                                                     | 00H        |

| 05~04H       | VID          | Vendor ID, high byte after, arbitrary value                                                                                                                                              | 1A86H      |

| 07~06H       | PID          | Product ID, high byte is behind, any value                                                                                                                                               | 55??H      |

| 09~08H       | RID          | Release ID, high byte is behind, any value                                                                                                                                               | 0100H      |

| 17~10H       | SN           | Serial Number, Product serial number string, length 8                                                                                                                                    | 12345678   |

| 7511 2011    | DID          | Printer port: according to the device ID string of the printer defined by IEEE-1284                                                                                                      | 0011 0011  |

| 7FH~20H      | PIDS         | Serial port or parallel port: non-printer product description string                                                                                                                     | 00H, 00H   |

| Others       |              | (Reserved)                                                                                                                                                                               | 00H or FFH |

The following table is the content of the external serial EEPROM configuration chip.

The following table is the specific configuration defined by CFG, explained by bit.

| Bit Address | Abbreviation | Description                                                                                                                                                                                                                                                            | Default |

|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7           | PRT          | Select communication interface: For serial port, this value<br>must be 1.<br>For non-serial port selection: 0=standard USB printer port;<br>1=parallel port                                                                                                            | 1       |

| 6           | PWR          | USB device power supply mode: 0=external and USB;<br>1=USB bus only                                                                                                                                                                                                    | 1       |

| 5           | SN-S         | Product serial number string: 0=valid; 1=invalid                                                                                                                                                                                                                       | 1       |

| 4           | DID-S        | The device ID string of the printer: 0=valid; 1=invalid                                                                                                                                                                                                                | 1       |

| 4           | PID-S        | Non-printer product description string: 0=valid; 1=invalid                                                                                                                                                                                                             | 1       |

| 3           | SPD          | Data transmission speed of the print port: 0=high speed;<br>1=low speed/standard                                                                                                                                                                                       | 1       |

| 2           | SUSP         | Automatic suspend and low power consumption when USB is idle: 0=disable; 1=allow                                                                                                                                                                                       | 1       |

| 1<br>0      | PROT         | Define the interface protocol in the configuration<br>descriptor of the USB device:<br>For serial or parallel ports, the effective value is 0 to 3, and<br>0 is recommended.<br>For a standard USB printer port, the valid values are 1 and<br>2, and 2 is recommended | 1<br>0  |

### **5.4 UART**

The pins of CH341 chip in asynchronous serial port mode include: data transmission pin, hardware rate control pin, working status pin, MODEM contact signal pin, auxiliary pin.

Data transmission pins include: TXD pin and RXD pin. TXD and RXD should be high when the serial port is idle.

The hardware rate control pins include: TEN# pin and RDY# pin. TEN# is the serial port transmission enable. When it is high, CH341 will suspend sending data from the serial port until TEN# is low. The RDY# pin is ready for serial port reception. When it is high, it means that CH341 is not ready to receive and cannot receive data temporarily. It may be that the chip is resetting, the USB has not been configured or has been unconfigured, or the serial port receiving buffer has been Full wait.

Working status pins include: TNOW pin and ROV# pin. TNOW indicates that CH341 is sending data from the serial port with a high level, and it is a low level after the transmission is completed. In the half-duplex serial port mode, TNOW can be used to indicate the serial port transceiver switch status. ROV# indicates with low level that the built-in serial port receiving buffer of CH341 is about to or has overflowed, and the following data may be discarded. Under normal circumstances, the receiving buffer will not overflow, so ROV# should be high.

MODEM contact signal pins include: CTS# pin, DSR# pin, RI# pin, DCD# pin, DTR# pin, RTS# pin. All these MODEM communication signals are controlled by computer application program and define their purpose, rather than directly controlled by CH341. If a faster rate control signal is required, hardware rate signal can be used instead.

The auxiliary pins include: INT# pin, OUT# pin, IN3 pin and IN7 pin. INT# is a custom interrupt request input. When it detects a rising edge, the computer will receive a notification; OUT# is a general-purpose low-level effective output signal, and the computer application can set its pin status. These auxiliary pins are not standard serial port signals, and their use is similar to MODEM communication signals.

CH341 has built-in independent receive and receive buffer, which supports simplex, half duplex or full duplex asynchronous serial communication. Serial data includes 1 low level start bit, 5 to 9 data bits, 1 or 2 high level stop bits. It supports odd / even check / flag check / blank check. CH341 supports common communication baud

rate error of the serial port receiving signal is about 2%.

rates: 50, 75, 100, 110, 134.5, 150, 300, 600, 900, 1200, 1800, 2400, 3600, 4800, 9600, 14400, 19200, 28800, 33600, 38400, 56000, 57600, 76800, 115200, 128000, 153600, 230400, 460800, 921600, 1500000, 2000000, etc. The baud rate error of the serial port sending signal under the external clock mode is less than 0.3%, the baud rate error of the serial port sending signal under the built-in clock mode is less than 1.3%, and the allowable baud

In the Windows operating system on the computer side, the driver of CH341 can emulate a standard serial port, so most of the original serial port applications are completely compatible and usually do not need to be modified. In addition, CH341 also supports indirect access to the external serial EEPROM memory of CH341 through standard serial communication.

CH341 can be used to upgrade the original serial peripheral equipment, or to add additional serial ports to the computer through the USB bus. By adding level conversion devices, it can further provide RS232, RS485, RS422 and other interfaces.

#### **5.5 Print Port**

In the print port mode, the pins of the CH341 chip can refer to the signals of the standard Centronic printer interface.

CH341 provides a standard USB printer port, compatible with USB specifications and IEEE-1284 specifications and Windows operating system. No driver is required under Windows 2000, XP and Vista operating systems on the computer (the actual situation is that Windows has its own driver). Drivers and applications that support printing are fully compatible and do not require any modification.

The printer port of CH341 supports two USB printer interface protocols, which can be defined in the external EEPROM configuration chip. The interface protocol is specified through the configuration descriptor of the USB device: PROT=1 is a one-way transmission interface, and PROT=2 is a two-way transmission interface. By default, CH341 selects a two-way transmission interface, and the data transmission efficiency is slightly higher than that of a one-way interface, which conforms to the IEEE-1284 specification.

The print port of CH341 supports two data transmission speeds: low-speed printing mode (standard printing mode) and high-speed printing mode. In low-speed mode, CH341 needs to detect the printer's response signal ACK# and busy state signal BUSY, and the effective width of the data strobe pulse STB# is 1uS, and the data transmission speed in the ideal state is 500KB/S. In the high-speed mode, the effective width of the data strobe pulse STB# is 0.5uS, and the data transmission speed in an ideal state is 800KB/S.

CH341 can be used to convert various standard original parallel printers into USB printers.

## 6. Parameters

#### 6.1. Absolute Maximum Ratings

(critical state or exceeding maximum can cause chip to not work or even be damaged)

| Name | Parameter Description               |                                       |         | Max. | Unit |

|------|-------------------------------------|---------------------------------------|---------|------|------|

| TA   | TA Operating Ambient<br>Temperature | CH341B/F/C/A/T/H chip, external clock | -40     | 85   | °C   |

|      |                                     | CH341B/F/C chip, built-in clock       | -20     | 70   | °C   |

| TS   | Storage Temperature                 |                                       |         | 100  | °C   |

| VCC  | Supply Voltage(VCC c                | -0.5                                  | 6.5     | V    |      |

| VIO  | The voltage                         | -0.5                                  | VCC+0.5 | V    |      |

#### **6.2. Electrical Parameters**

(test conditions: TA=25°C, VCC=5V, exclude pins connected to USB bus) (all the current parameters should multiply the coefficient of 40% when the supply voltage is 3.3V)

| Name  |                                                                                     | Parameter Description       |                              |         | Typical | Max.    | Unit |  |

|-------|-------------------------------------------------------------------------------------|-----------------------------|------------------------------|---------|---------|---------|------|--|

|       |                                                                                     | V3 doesn't                  | connect to VCC               | 4.0     | 5       | 5.5     |      |  |

| VCC   | VCC Supply<br>Voltage                                                               | V3 connects to<br>VCC       | External clock               | 3.0     | 3.3     | 3.6     | v    |  |

|       |                                                                                     |                             | CH341B/F/C<br>built-in clock | 3.1     | 3.3     | 3.6     |      |  |

|       |                                                                                     | ng Supply<br>mal Operation) | CH341A/T/H chip,<br>VCC=5V   |         | 12      | 30      | mA   |  |

| ICC   |                                                                                     |                             | CH341B/F/C chip,<br>VCC=5V   |         | 8       | 20      |      |  |

|       |                                                                                     |                             | VCC=3.3V                     |         | 6       | 15      |      |  |

| ICI D | Operating Supply                                                                    | ng Supply                   | VCC=5V                       |         | 0.12    | 0.25    |      |  |

| ISLP  | Current(US                                                                          | Current(USB Suspend)        |                              |         | 0.04    | 0.12    | mA   |  |

| VIL   | Input Low Voltage                                                                   |                             |                              | -0.5    |         | 0.7     | V    |  |

| VIH   | Input High Voltage                                                                  |                             |                              | 2.0     |         | VCC+0.5 | V    |  |

| VOL   | Output Low Voltage(5mA draw current)                                                |                             |                              |         |         | 0.5     | V    |  |

| VOH   | Output High Voltage(4mA output current)<br>(Output 100uA current during chip reset) |                             |                              | VCC-0.5 |         |         | V    |  |

| IUPs  | High-level output current of SCL and SDA pins                                       |                             | 100                          | 200     | 500     | uA      |      |  |

| IUP   | Draw current of input with integrated pull-up resistor                              |                             |                              | 3       | 120     | 250     | uA   |  |

| IDN   | Draw current of input with integrated pull-down resistor                            |                             |                              | -40     | -100    | -250    | uA   |  |

| VR    | Voltage                                                                             | threshold when p            | ower-up reset                | 2.1     | 2.6     | 2.8     | V    |  |

## 6.3. Basic timing parameters

(test conditions: TA=25°C, VCC=5V or VCC=V3=3.3V)

| Name  | Parameter Description                                | Min.  | Тур.  | Max.  | Unit |

|-------|------------------------------------------------------|-------|-------|-------|------|

| FCLK  | Frequency of input clock in XI                       | 11.98 | 12.00 | 12.02 | MHz  |

| FCLK0 | CH341B/F/C internal frequency in built-in clock mode | 11.76 | 12.00 | 12.04 | MHz  |

| TPR   | Reset time of power-up                               | 9     | 20    | 40    | mS   |

| TRI   | Effective signal width of external reset input       | 100   |       |       | nS   |

| TRD   | Reset delay after external reset input               |       | 30    |       | mS   |

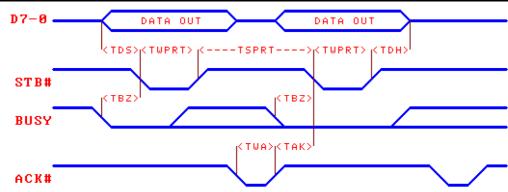

## 6.4. Print port timing parameters

(Test conditions: TA=25°C, VCC=5V or VCC=V3=3.3V, refer to the attached picture)

| Name  | Parameter Description             |           | Min. | Тур. | Max.  | Unit |

|-------|-----------------------------------|-----------|------|------|-------|------|

| TWPRT | Data strobe STB# active low width | Low speed | 800  | 840  | 10000 | nS   |

|         |                                                         | High speed | 400 | 420 | 10000 | nS |

|---------|---------------------------------------------------------|------------|-----|-----|-------|----|

| TSPRT D | Data strobe STB# high level interval width              | Low speed  | 800 |     |       | nS |

|         |                                                         | High speed | 560 |     |       | nS |

| TDS     | STB#Data establishment time before valid                |            | 240 |     |       | nS |

| TDH     | Data retention time after STB# is valid                 |            | 240 |     |       | nS |

| TBZ     | Busy state BUSY low level to STB# effective             |            | 160 |     |       | nS |

| TWA     | Active low width of ACK#                                |            | 100 |     |       | nS |

| TAK     | Receive response ACK# is valid from rising edge to STB# |            | 160 |     |       | nS |

## 7. Applications

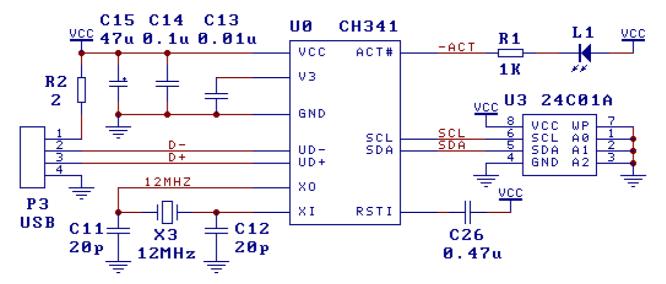

#### 7.1. Basic connection/external clock (picture below)

P3 is the USB port. The USB bus includes a pair of 5V power lines and a pair of data signal lines. Usually, the +5V power line is red, the ground line is black, the D+ signal line is green, and the D- signal line is white. The power supply current provided by the USB bus can usually reach 500mA. In general, the CH341 chip and low-power USB products can directly use the 5V power supply provided by the USB bus. If the USB product provides the standing power supply through other power supply methods, then CH341 should also use the standing power supply. If you need to use the USB bus power supply at the same time, you can connect the 5V power line of the USB bus to the USB product's 5V power line through a resistance of about  $1 \Omega$ . 5V standing power supply, and the grounding wires of the two are directly connected.

C13 and C14 are monolithic or high-frequency ceramic capacitors. The capacity of C13 is  $0.01 \,\mu$  F to  $0.1 \,\mu$  F, used for decoupling the internal power node of CH341, and the capacity of C14 is  $0.1 \,\mu$  F, which is used for

decoupling external power.

The crystal X3, capacitors C11 and C12 are used for the clock oscillation circuit. The frequency of X3 is 12MHz, C11 and C12 are monolithic or high-frequency ceramic capacitors with a capacity of  $15pF \sim 30pF$ .

If you replace CH341A/T with the CH341B/C chip with built-in clock for the existing finished board designed based on the CH341A/T chip, you can remove X3 and C11, and short-circuit C12 or replace it with a  $0 \Omega$  resistor.

If the USB product uses USB bus power and a large capacitor C15 is connected in parallel between VCC and GND, which makes the power-on process slower and the power cannot be discharged in time after the power is off, then CH341 will not be able to reset reliably. A capacitor C26 with a capacitance of  $0.1 \,\mu$  F or  $0.47 \,\mu$  F can be connected across RSTI pin and VCC to extend the reset time.

The LED L1 and the current limiting resistor R1 are optional components and are usually omitted. The external serial EEPROM configuration chip U3 is an optional device. When U3 is omitted, the chip function can be selected through the combination of SCL and SDA pins.

When designing the printed circuit board PCB, you need to pay attention: the decoupling capacitors C13 and C14 should be as close as possible to the connecting pins of CH341; make the D+ and D- signal lines close to parallel wiring, and try to provide ground wires or copper on both sides to reduce external sources Signal interference; try to shorten the length of the signal lines related to the XI and XO pins. In order to reduce high-frequency interference, you can surround the ground wire or copper around the relevant components.

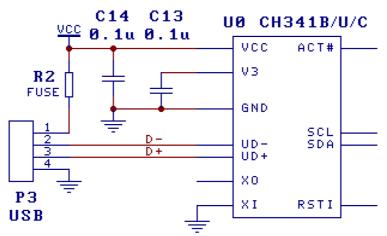

#### 7.2. Simplified basic connection/internal clock (picture below)

If the CH341B/F/C chip with built-in clock is used, the external crystal and oscillation capacitor can be eliminated, and the circuit is more concise. Decoupling capacitors C13 and C14 are necessary. When designing the PCB, they should be as close as possible to the connecting pins of CH341.

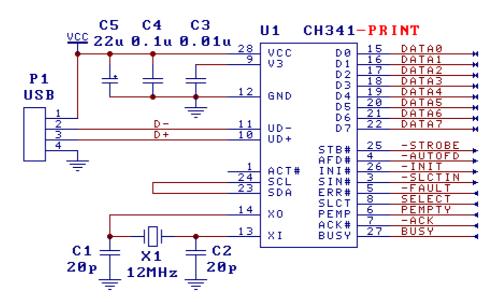

#### 7.3. Convert parallel port printer (picture below)

In the figure, the SDA pin is connected to the SCL pin, so that CH341 is configured as a standard USB printer port, which is used to convert a parallel printer to a USB printer. The signal line on the right in the figure corresponds to the signal line of IEEE-1284 specification or standard Centronic printer interface.

In practical applications, considering impedance matching, it is recommended to refer to the requirements in the IEEE-1284 specification, add pull-up resistors with a resistance of about  $2K \Omega \sim 5K \Omega$  to each signal line of the printer port, and connect each signal line of the printer port in series The resistance of about  $20 \Omega \sim 40 \Omega$  is connected to the original parallel printer.

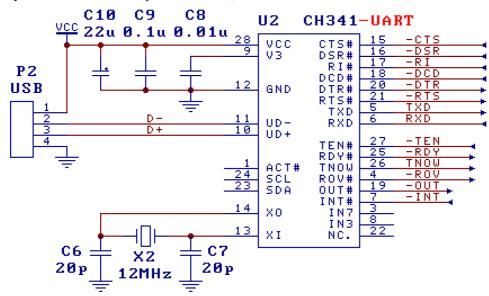

#### 7.4. USB to TTL asynchronous serial port (picture below)

In the figure, the SDA pin and SCL pin are left floating, so that CH341 is configured as an asynchronous serial port. The signal line on the upper right part of the figure corresponds to the commonly used serial port signal and MODEM signal. After the TTL level is converted to RS232 level through MC1488/MC1489, MAX232/ICL232 or MAX213/ADM213/SP213, it can be further converted to RS232C serial port .

The signal wires on the right side of the figure can only be connected to RXD, TXD, TEN# and the common ground wire. Other signal wires can be selected as needed and can be left floating when not needed. Since CH341 can only send when the TEN# pin is low level, so TEN# should be connected to low level or GND.

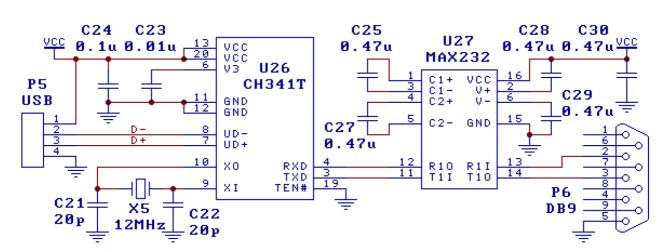

#### 7.5. USB to 3-wire RS232 serial port (picture below)

The picture shows the USB to RS232 serial port, P6 is the DB9 pin, this 3-wire serial port is the most basic and most commonly used asynchronous serial port.

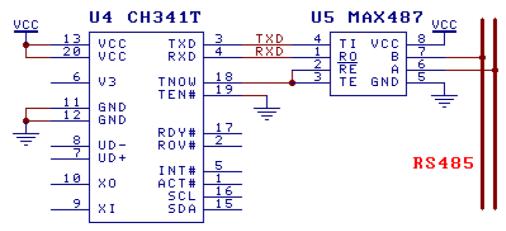

#### 7.6. USB to RS485 interface (picture below)

Refer to the basic connection diagram for crystal, oscillation capacitor, and power decoupling capacitor. TEN# is directly grounded, so CH341 is always allowed to send through the serial port. TNOW is used to control the transceiver status of the RS485 bus half-duplex transceiver U5.

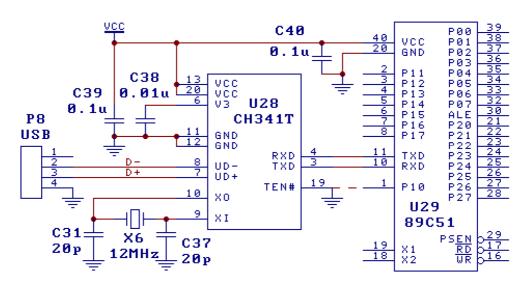

#### 7.7. Connect to the serial port of the microcontroller (picture below)

In the picture, the single-chip microcomputer/MCU is connected to CH341 through the serial port to realize the USB communication between the single-chip microcomputer and the computer.

If the baud rate of the serial communication is high or the microcontroller is too late to receive, then any output pin of the microcontroller can be used to control the TEN# pin of CH341. When the microcontroller is idle and can receive serial data, set TEN# to low level. When it is busy or inconvenient to receive serial port data, set TEN# to high level to make CH341 suspend sending the next byte to realize rate control.

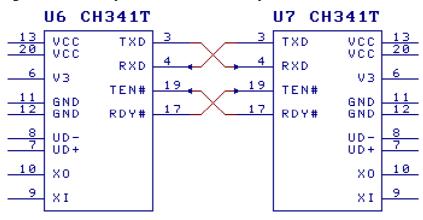

#### 7.8. Serial port connection (picture below)

The RDY# pin of one's own side is connected to the other's TEN# pin. Only when one's own party is ready to receive, the other party can send. Therefore, no matter how high the serial port communication rate is, both parties can keep data synchronization without losing data. If the serial port communication rate is high, or the speeds of both parties do not match, or the low-speed MCU is connected to the serial port of CH341, the hardware rate control signal should usually be used to ensure data synchronization.