Bonjour, j'ai un petit soucis avec du transfert DMA :

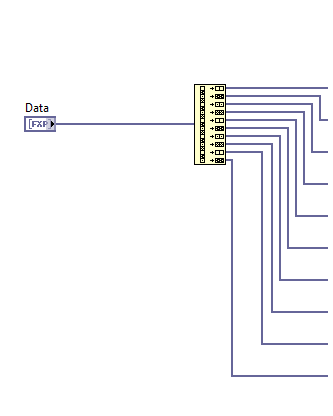

- Couche FPGA : acquisition de données simultanée de données -> transfert DMA

dans une boucle for avec un cadencement.

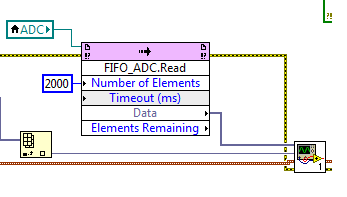

- Couche RT : je dépile la DMA

Dans une boucle cadencée.

Problème, je loupe une donnée dans mon dépouillement et du coup les données dépilée ne sont plus dans l'ordre attendues ! Le problème c'est que lorsque je lance le programme, tout va bien et au bout d'un moment (aléatoire) ça déraille.

Merci !

Répondre avec citation

Répondre avec citation

Partager